# XMC-FZU Series Configurable Zyng® UltraScale+™ MPSoC with Plug-In I/O

AMD Zyng® ZU7EV MPSoC ◆ ARM Cortex™ A53 & R5 CPUs ◆ Programmable logic ◆ Air/Conduction-Cooled

XMC-FZU series modules provide a programmable Xilinx Zynq UltraScale+ multiprocessor system on a chip (MPSoC). This MPSoC combines a feature-rich ARM-based processing system and programmable logic in a single device. Two multi-core ARM Cortex CPUs (A53 application processor and R5 real-time processor) deliver high-performance computation capability. Additional resources include on-chip memory, external memory interfaces, and a rich set of peripheral connectivity interfaces. The integrated ASIC-class programmable logic is ideal for computeintensive tasks and offloading critical applications.

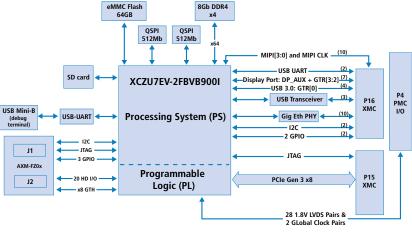

An AXM-FZU01 expansion I/O module with dual QSFP+ ports plugs in to interface high-speed signals, such as 10GbE, to the programmable logic. Other AXM mezzanine modules can support a variety of fiber optic or LVDS I/O interfaces.

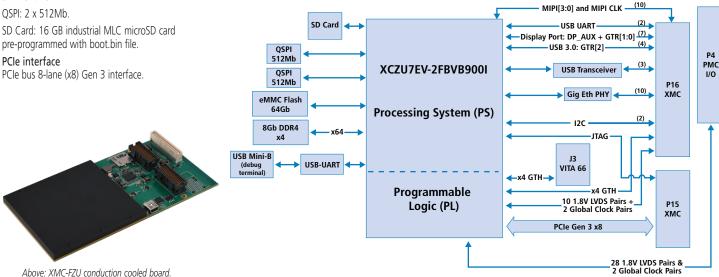

The rear XMC connectors route peripheral I/O to the processor system and high-speed serial lanes for PCIe, Serial RapidIO or 10-Gigabit Ethernet. Additional user I/O such as high speed serial, LVDS or global clock signals can also access the programmable logic over the rear connectors.

The real value of the Zyng UltraScale+ MPSoC architecture lies in the tight integration of its programmable logic with the processing system. Its high throughput interface eliminates bottlenecks that plague two-chip ASSP-FPGA solutions and allows designers to easily extend the processing system capabilities. Now developers can build custom designs by adding peripherals in the programmable logic and increase overall system performance by partitioning hardware and software functions with custom accelerators.

Designed for COTS applications these MPSoC I/O modules deliver user-customizable I/O in a high-density and very rugged form factor. Typical applications involve adaptive filtering, sensor fusion, motor control, and image processing.

Acromag's Engineering Design Kit (EDK) provides example designs that provides host access to the hardware I/O. The examples are implemented using the Xilinx Vivado® development environment and offer a starting point from which customers can develop their customized applications. Vitis® and PetaLinux® examples are also provided.

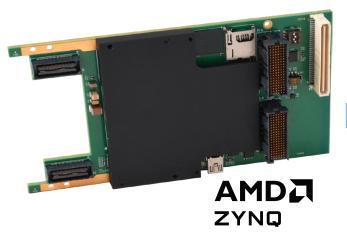

Above: XMC-FZU board shown with optional AXM plug-in I/O expansion module, At left: AXM-FZU01 I/O breakout board.

# **Key Features & Benefits**

# Zynq MPSoC

- Quad-core ARM Cortex A53-based application processing unit (APU)

- Dual-core ARM Cortex R5-based real-time processor unit (RPU)

- Mali<sup>™</sup>-400 GPU

- H.264/265 video codec

- UltraScale+ 504k programmable logic cells

- Extensive on-chip memory

# I/O and Peripherals

- Gigabit Ethernet interface

- USB 3.0 and USB-UART ports

- DisplayPort

- LVDS I/O

## General

- PCI Express Gen 3 x8 interface

- MicroSD or NOR flash boot

- Dual Quad-SPI flash memory

- 8GB DDR4 storage memory

- DMA transfers

- BSP and MPSoC design kit software

- VxWorks®, Linux®, and Windows® support

Tel 844-878-2352 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 S. Wixom Rd, Wixom, MI 48393-2417 USA

# **Performance Specifications**

# Multiprocessor SoC

### MPSoC device

AMD (Xilinx) Zynq XCZU7EV-2FBVB900I

Application processor: Quad-core ARM Cortex-A53, up to 1.5GHz.

Real-time processor: Dual-core ARM Cortex-R5, up to 600MHz.

GPU: Mali™-400 MP2 up to 667MHz.

Video Codec: H.265/H.264

Programmable Logic: 504k logic cells; 230k LUTs; 1728 DSP slices.

# Configuration

Primary boot from SD card or NOR flash alternate.

# I/O and Peripheral Interfaces

#### AXM Mezzanine I/O

AXM modules plug into the XMC module's front mezzanine for additional I/O lines. Analog, digital, and peripheral I/O AXM modules are sold separately.

### Front I/O to Programmable Logic

AXM J1 & J2: 20 high-performance 1.8V I/O, 8 GTH 16.3Gb/s lines.

# Rear I/O to Programmable Logic

P4: 30 LVDS pairs, 2 global clock pairs.

P15: 8 high-speed (16.3Gb/s) serial lanes for PCIe. Serial RapidIO, or 10GbE.

P16 (conduction-cooled models only):

10 high-performance 1.8V I/O, 4 GTH 16.3Gb/s lines.

J3 (conduction-cooled models build option): VITA 66-compatible MT-ferrule fiberoptic transceiver for 4 GTH 16.3Gb/s lines (consult factory).

# Rear I/O to Processing System

P16: Tri-mode Gigabit Ethernet 10/100/1000, USB 3.0, USB-UART, DisplayPort, 3 GTR 6Gb/s lines.

# Memory

DDR4: 8GB. eMMC: 64GB.

#### PCle interface

## Environmental

# Operating temperature

Air-cooled (with heat spreader): 0 to 70°C (minimum airflow of 400LFM is recommended). Conduction-cooled: -40 to 85°C.

### Storage temperature

-55 to 125°C

# Relative humidity

5 to 95% non-condensing.

#### Power

3.3V DC (±5%): 150 mA typical 3.3V AUX (±5%): 10 mA typical VPWR (+12V DC): 1000 mA typical +12V DC (±5%): TBD mA typical -12V DC: not used.

# Vibration, sinusoidal operating

VITA 47 Class V2, per MIL-STD-810 Method 514. 5g peak, 1 hour per axis from 5 to 2000 Hz.

#### Vibration, random operating

VITA 47 Class V2, per MIL-STD-810 Method 514. 5 to 100 Hz PSD increasing at 3 dB/octave. 100 to 1000 Hz PSD =  $0.04 \text{ g}^2/\text{Hz}$ . 1000 to 2000 Hz PSD decreasing at 6 dB/octave.

### Shock, operating

VITA 47 Class OS2, per MIL-STD-810 Method 516. 40g peak, 11 ms, half-sine. 40g peak, 11 ms, sawtooth, all three axes.

# Mean time between failure (MTBF)

MIL-HDBK-217F, FN2. Ground benign, controlled. Consult factory for details.

# Engineering Design Kit

Board support package and FPGA design kit for AMD Vivado®, Vitis™, and PetaLinux. Includes schematics, part location drawings, and example design files.

Kit must be ordered with the first purchase of an XMC-ZU module (see www.acromag.com for more information).

# **Ordering Information**

#### Models

# Go to on-line ordering page >

#### XMC-FZU7EV-42-30

XMC module with XCZU7EV and AXM front I/O connectors, rugged air-cooled.

## XMC-FZU7EV-42-50

XMC module with XCZU7EV and rear I/O (no AXM connectors), conduction-cooled.

#### Software

# XMC-FZU-EDK

Engineering design kit. (One kit required)

# PMCSW-API-VXW

VxWorks® software support package.

#### PCISW-API-WIN

Windows® software support package.

#### PMCSW-API-LNX

Linux™ software support. (website download only)

# **Accessories**

### AXM-FZU01

AXM module with dual QSFP+ ports

#### AXM-??

Custom I/O configurations available, call factory.

#### Carrier Cards

See a full list of XMC carrier cards.