## **Embedded Computing & I/O Solutions**

# **Reconfigurable FPGA Modules**

mPCle-based, XMC, PMC or Industry Pack Formats

> Faster & Easier **Development**

> > **Engineering Design Kit**

# **Depend on Acromag**

especially when

engineering the right

embedded solution.

And with more than

60 years experience,

Acromag can help

you reduce your

costs and increase

your productivity.

## **Acromag: The I/O Leader**

Acromag is focused on developing embedded computing solutions that provide the best long term value in the industry. Compare and you will find that Acromag offers an unmatched balance of price, performance, and features.

## **60+ Years of I/O Experience**

With over 60 years of industrial I/O design experience, Acromag stands alone in the high-performance bus-board market. Developing VMEbus I/O boards since 1984, we combine our process control expertise with extensive experience in embedded computing. This background gives us unrivaled insight to many unique concerns when interfacing computer systems to various sensors and controllers in a wide range of applications.

Acromag processor, FPGA, and I/O products are commonly used in these industries:

- military/defense

- transportation

- semiconductors

- communication

- aerospace

- manufacturing

- scientific

- research labs

### **Quality You Can Count On**

We take every measure to guarantee dependable operation with ISO9001 and AS9100 certified quality management. State-of-the-art manufacturing with industrial-grade components adds extra ruggedness. Advanced inspection and testing further ensure that Acromag I/O performs at or beyond their rated specs.

### **Technical Support**

Drawing on a wealth of embedded I/O experience, our sales engineers are well qualified to support you in the use of our products in your end-applications. We take pride in our highly experienced staff that excels at after-sale technical support.

### **Global Representation**

Great care has been put into building a team of highly skilled representatives and distributors. They are located around the world to service your needs.

### **Online Ordering**

Find full documentation and pricing information online. You can get quotes and even order directly on our website.

- f Become a fan: www.facebook.com/acromaginc

- Follow us: www.twitter.com/acromag

- (n) Connect with us: www.linkedin.com/company/acromag

- Subscribe to our channel: www.youtube.com/acromagio

Acromag, Incorporated • 30765 South Wixom Road • Wixom, Michigan 48393 • USA

# FPGAs Made Easy

Above: APCe7022 PCIe carrier card shown with the APA7-500

Do you want to learn how to implement FPGAs? Think the only way is with a high start-up price tag and complicated setup? Think again.

Acromag offers you an easy, cost-effective package to start your FPGA development today.

### Custom Embedded Computing with Re-Configurable FPGAs on Off-the-Shelf Mezzanine Modules

Acromag's line of user-configurable FPGA I/O modules offer the ability to create custom I/O boards. Just download your own instruction sets into the I/O module's FPGA. You can use your own application program to control the module's analog or digital I/O channels for simulation, communication, diagnostics, image processing and other applications.

### Faster and Easier Development

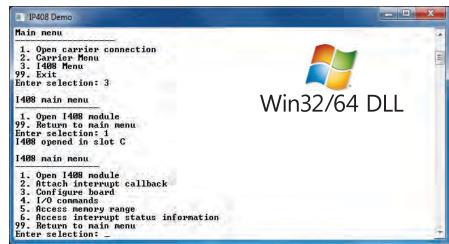

To help you develop custom programs, Acromag offers an Engineering Design Kit. This kit provides utilities to help you load VHDL into the FPGA and to establish DMA transfers between the FPGA and the CPU. Kits include a compiled FPGA file and example VHDL code for the local bus interface, read/writes, and change-of-state interrupts to the bus.

### **What You Will Need:**

Choose your FPGA module

XMC-SLX Series Spartan®-6 FGPA Modules XMC-7A Series Artix®-7 FGPA Modules

**XMC-7K Series** Kintex®-7 FGPA Modules

**APA7 Series** Artix-7 FGPA Modules

**APZU Series** Zync<sup>®</sup> UltraScale+™ MPSoC FGPA Modules

Select your carrier card

**APCe8675** PCI Express Carrier Card **APCe7000** AcroPack® mPCle-based Carrier Cards

- XMC or AcroPack module slots

- Up to 8-lanes of PCle-based support depending on carrier

- Support high-speed serial interface between neighboring cards using protocols such as XAUI or Aurora

- JTAG support for FPGA programming

Add your EDK

Pick your OS

### **EDK** Engineering Design Kit

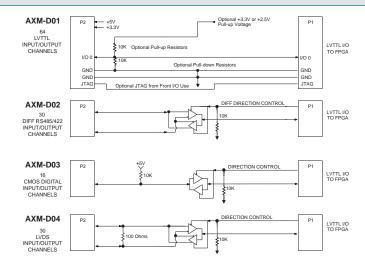

- Includes AXM-EDK extension module providing standard JTAG header and LVTTL I/O

- Includes parts list and location, schematics, complied FPGA file and example VHDL code

- Loads VHDL code and establishes DMA transfers to CPU

The AXM-EDK front I/O extension module includes a JTAG interface and LVTTL I/O for application interface or debugging purposes.

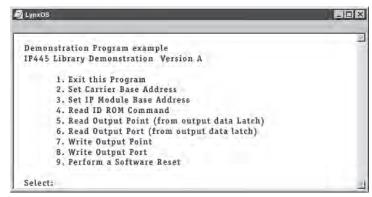

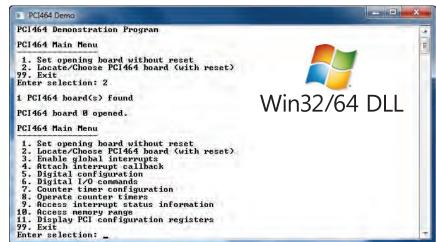

### **Software Support Package**

- For XMC: PCISW-API-WIN Windows® DLL | PCISW-API-LNX Linux® | PMCSW-API-VXW VxWorks®

- For AcroPack: APSW-API-VXW VxWorks | APSW-API-WIN Windows DLL | APSW-API-LNX Linux

Tel 844-878-2352 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 Wixom Rd, Wixom, MI 48393 USA

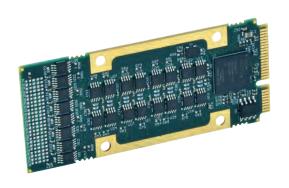

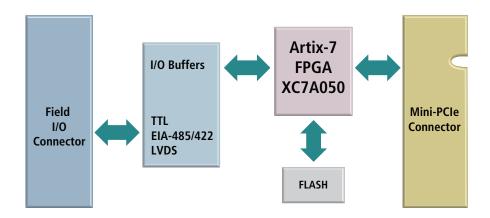

## APA7 Series User-Configurable Artix®-7 FPGA I/O Modules

Reconfigurable Xilinx<sup>®</sup> Artix<sup>®</sup>-7 FPGA ◆ Conduction or Air Cooled ◆ PCIe Bus Interface

### **Description**

### Models

**APA7-501E-LF:** 48 TTL channels **APA7-502E-LF:** 24 EIA-485/422 channels

APA7-503E-LF: 24 TTL and

12 EIA-485/422 channels

APA7-504E-LF: 24 LVDS channels

The AcroPack® product line updates our popular Industry Pack I/O modules with a PCIe interface format. This tech-refresh design offers a compact size, low-cost I/O, the same functionality as the existing Industry Pack modules and a rugged form factor.

The APA7-500 series provides a FPGA based user-configurable bridge between a host processor and a custom digital interface via PCI Express. These boards feature a best in class Artix®-7 interface to deliver the industry's lowest power and high performance.

Designed for COTS applications these FPGA based digital I/O modules deliver user-customizable I/O, high-density, high-reliability, and high-performance at a low cost.

The APA7-500 series modules are 70mm long. This is 19.05mm longer than the full length mini PCle card at 50.95mm. The boards width is the same as mPCle board of 30mm and they use the same mPCle standard board hold down standoff and screw keep out areas.

A down facing 100 pin Samtec connector mates with the carrier card. Fifty of these pins are available for field I/O signals.

The Engineering Design Kit provides users with basic information required to develop custom FPGA firmware for download to the Xilinx FPGA. Example FPGA design code is provided as a Vivado IP Integrator project for functions such as a one-lane PCI Express interface, DMA, digital I/O control register, and more. Users should be fluent in the use of Xilinx Vivado design tools.

### **Key Features & Benefits**

- PCI Express Generation 1 interface

- Reconfigurable Xilinx® FPGA

- High channel count digital interface: RS485, LVDS and TTL interface options.

- 32Mb quad serial Flash memory

- 52,160 logic cells

- 65,200 Flip flops

- 2,700 kb block RAM

- 120 DSP slices

- External LVTTL clock input

- Long distance data transmission

- Example design

- Power up and systemd reset is failsafe

- Conduction-cooled options

### **Performance Specifications**

#### FPGA

FPGA device

Xilinx Artix-7 FPGA Model XC7A50T.

FPGA configuration

Download via flash memory.

Example FPGA program

IP integrator block diagram provided for PCIe bus 1 lane Gen 1 interface, DMA controller, on chip block RAM, flash memory and control of field I/O. See EDK kit.

### ■ I/O Processing

Field I/O Interface

PCIe bus 1 lane Gen 1 interface.

I/O Connector

100 pin field I/O connector.

### **■** Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a APA7-500 series module (see www.acromag.com for more information).

### ■ PCI Express Base Specification

Conforms to revision 2.0

Lanes

1 lane in each direction.

**Bus Speed**

2.5 Gbps (Generation 1).

Memory

128k space required.

1 base address register.

### Environmental

Operating temperature

Air Cooled with heat sink

-40 to 80°C.

Air Cooled without heat sink

-40 to 70°C.

Conduction Cooled

-40 to 85°C.

A conduction cooled application with an AcroPack requires heatsink model AP-CC-01.

Storage temperature

-55 to 125℃

Relative humidity

5 to 95% non-condensing.

Power

+3.3V (±5%) 500mA typical.

### Physical

Length

70mm.

Width 30mm.

### **Ordering Information**

### AcroPack® Modules

APA7-501E-LF

48 TTL channels.

APA7-502E-LF

24 EIA-485/422 channels.

APA7-503E-LF

24 TTL & 12 EIA-485/422 channels.

APA7-504E-LF

24 LVDS channels.

(Note: AcroPack modules are compatible only with the carriers listed below)

#### Accessories

AP-CC-01

Conduction-cool kit.

APA7-EDK

Engineering design kit. (One kit required)

#### **Carrier Cards**

See <u>Acromag.com/AcroPack-Carriers</u> for a full list of AcroPack carrier cards.

**Software** (see software documentation for details)

APSW-API-VXW

VxWorks® software support package.

**APSW-API-WIN**

Windows® DLL driver software support package.

**APSW-API-LNX**

Linux® support (website download only).

AP-CC-01 Conduction-Cool Kit

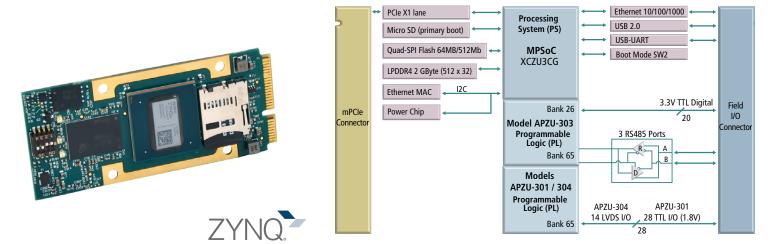

## **APZU Series** User-Configurable Zyng® UltraScale+™ MPSoC I/O Modules

Xilinx® Zynq UltraScale+™ MPSoC ◆ ARM Cortex™ A53 & R5 CPUs ◆ Programmable logic ◆ PCIe Bus Interface

### **Models**

APZU-301: 28 TTL I/O

APZU-303: 20 TTL and 3 RS485/422

APZU-304: 14 LVDS I/O

### **Description**

AcroPack® modules are a ruggedized version of a mini PCIe card. AcroPacks add a down-facing 100-pin connector to internally route I/O signals through the carrier card to secure field connectors, thus eliminating loose cables and increasing reliability.

APZU series modules provide a programmable Xilinx Zynq UltraScale+ multiprocessor system on a chip (MPSoC). This MPSoC combines a feature-rich ARM-based processing system and programmable logic in a single device. Two dual-core ARM Cortex CPUs (A53 application processor and R5 real-time processor) deliver high-performance computation capability. Additional resources include on-chip memory, external memory interfaces, and a rich set of peripheral connectivity interfaces. The integrated ASIC-class programmable logic is ideal for compute-intensive tasks and offloading critical applications.

The real value of the Zynq UltraScale+ MPSoC architecture lies in the tight integration of its programmable logic with the processing system. Its high throughput interface eliminates bottlenecks that plague two-chip ASSP-FPGA solutions and allows designers to easily extend the processing system capabilities. Now developers can build custom designs by adding peripherals in the programmable logic and increase overall system performance by partitioning hardware and software functions with custom accelerators.

Designed for COTS applications these FPGA-based digital I/O modules deliver user-customizable I/O in a high-density and very rugged form factor. Typical applications involve adaptive filtering, sensor fusion, motor control, and image processing.

Acromag's Engineering Design Kit (EDK) provides an FPGA generated firmware example design that provides host access to the hardware digital I/O on the APZU module. The example is implemented using the Xilinx Vivado® development environment and offers a starting point from which customers can develop their customized applications.

### **Key Features & Benefits**

### Zynq MPSoC

- Dual-core ARM Cortex A53-based application processor unit (APU)

- Dual-core ARM Cortex R5-based real-time processor unit (RPU)

- NEON<sup>™</sup> media-processing engine

- UltraScale+ 154k programmable logic cells

- Extensive on-chip memory

### I/O and Peripherals

- TTL, LVDS, or RS422/485 I/O interface

- Gigabit Ethernet interface

- USB 2.0 transceiver

- USB-UART debug terminal port

### General

- PCI Express interface

- MicroSD or NOR flash boot

- Quad-SPI flash memory

- LPDDR4 storage memory

- DMA transfers

- BSP and FPGA design kit software

- VxWorks®, Linux®, and Windows® support

Tel 844-878-2352 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 S. Wixom Rd, Wixom, MI 48393-2417 USA

### **Performance Specifications**

### Multiprocessor SoC

### MPSoC device

Xilinx Zyng XCZU3CG-2SBVA484I.

Application processor: Dual-core ARM Cortex-A53, 1.3GHz. Single/double precision floating point unit.

Real-time processor: Dual-core ARM Cortex-R5, 533MHz. Single/double precision floating point unit.

NEON Advanced SIMD media-processing engine.

Programmable logic resources:

154,350 logic cells; 70,560 LUTs; 360 DSP slices.

### Configuration

Primary boot from SD card or NOR flash alternate.

### I/O and Peripheral Interfaces

#### I/O connector

68 pin field I/O (to carrier card).

#### Digital I/O

APZU-301: 28 TTL I/O channels (1.8V).

APZU-303: 20 TTL and 3 RS485/422 channels (3.3V).

APZU-304: 14 LVDS I/O channels.

20 channels of interrupts configurable for high-to-low, low-to-high, and change-of-state event types.

#### LPDDR Memory

2 Gbyte (512Mbit x 32).

### Quad-SPI flash

512 Mbit (64 Mbyte) Nor flash device.

### SD card interface

16 GB industrial MLC microSD card pre-programmed with boot.bin file.

### Gigabit Ethernet interface

Supports 1000BASE-T, 100BASE-TX, and 10BASE-T. Zyng gigabit Ethernet controller uses a media independent interface (RGMII). External magnetics and RJ45 are provided on the breakout panel.

### USB 2.0 interface

Microchip USB3320C.

### **UART** to USB interface

Silicon Labs CP2103GM.

### Breakout panel

Model 5028-626 panel mates directly to all 68-pin AcroPack carriers. Brings RJ45 ethernet port, USB 2.0 port, UART to USB port, digital I/O at jumper blocks, and power and reset buttons out to the field.

### PCI Express

### Compatibility

Conforms to PCI Express Base Specification, Rev.2.1.

### PCle interface

PCIe bus 1-lane (x1) Gen 1 interface.

2.5 Gbps signaling rate.

### Memory space

1M Byte: BARO to Zyng DMA registers.

32K Byte: BAR1 to programmable logic register space.

64K Byte: BAR2 to DDR memory space.

### Environmental

### Operating temperature

Air-cooled (with heat spreader): -40 to 70°C (minimum airflow of 400LFM is recommended). Conduction-cooled: -40 to 80°C.

### Storage temperature

-55 to 125°C

### Relative humidity

5 to 95% non-condensing.

#### Power

3.3V DC (±5%): 57 mA typical, 100 mA max. 5.0V DC (±5%): 183 mA typical, 230 mA max. +12V DC (±5%): 165 mA typical, 200 mA max. 1.5V, -12V DC: not used.

### Vibration, sinusoidal operating

Designed to comply with IEC 60068-2-6.

### 10-500Hz, 5G, 2 hours/axis.

Vibration, random operating Designed to comply with IEC 60068-2-64. 10-500Hz, 5G-rms, 2 hours/axis.

#### Shock, operating

Designed to comply with IEC 60068-2-27. 30G, 11ms half sine; 50G, 3mS half sine; 18 shocks at 6 orientations for both test levels.

#### Mean time between failure (MTBF)

MIL-HDBK-217F, FN2. Ground benign, controlled.

25°C: 1,459,102 MTBF hours; 167 MTBF years; 685.4 failure rate (FIT).

40°C: 923,762 MTBF hours; 105.5 MTBF years; 1,082.5 failure rate (FIT).

FIT is failures in 109 hours.

### Physical

#### **Dimensions**

Length, width, height: 70 x 30 x 12.5 mm. Board thickness: 1.0 mm. Weight: 35.18 g (including heat spreader).

### Engineering Design Kit

Board support package and FPGA design kit for Xilinx Vivado®. Example of IP Block design, block RAM, system monitor, AXI interface to digital I/O.

Kit must be ordered with the first purchase of an APZU module (see <a href="https://www.acromag.com">www.acromag.com</a> for more information).

### **Ordering Information**

### AcroPack® Modules

Go to website product page for more information.

#### APZU-301

28 TTL channels (1.8V).

### APZU-301-OSP

Quick Start Package includes APZU-301 module, APCe7012 carrier, 5028-626 I/O panel, APZU-EDK software.

20 TTL & 3 EIA-485/422 channels (3.3V).

### APZU-303-QSP

Ouick Start Package includes APZU-303 module, APCe7012 carrier, 5028-626 I/O panel, APZU-EDK software.

### APZU-304

14 LVDS channels.

#### APZU-304-OSP

Quick Start Package includes APZU-304 module, APCe7012 carrier, 5028-626 I/O panel, APZU-EDK software.

### **Accessories**

#### APZU-EDK

Engineering design kit. (One kit required)

#### 5028-626

I/O breakout panel with cables for Ethernet, USB, UART, JTAG, and 68-pin carrier card connections.

#### **Carrier Cards**

See Acromag.com/AcroPack-Carriers for a full list of AcroPack carrier cards.

### Software

(see software documentation for details)

### APSW-API-VXW

VxWorks® software support package.

Linux® support (website download only).

### APSW-API-WIN

Windows® DLL driver software support package. APSW-API-LNX

APZU-30x with included heat spreader attached

### XMC-7A50-AP323 XMC Module with Artix®-7 FPGA and High-Density I/O

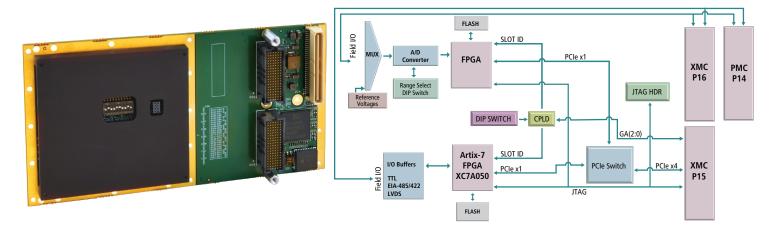

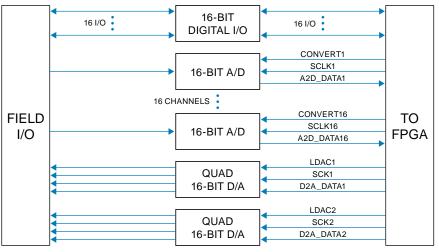

Reconfigurable Xilinx® Artix®-7 FPGA ◆ 48 Digital I/O ◆ 20 Diff or 40 SE Analog Inputs ◆ 16-bit ADC

### **Description**

XMC-7A51-AP323: 48 TTL channels

**Custom Requirements:** Other I/O combinations are possible, contact Acromag for more information. Build Option A: 24 EIA-485/422 channels Build Option B: 24 TTL and 12 EIA-485/422 channels Build Option C: 24 LVDS channels

Designed for COTS applications, these XMC modules combine a user-customizable FPGA with digital I/O and high-performance analog inputs for high-density signal processing.

The XMC-7A50-AP323 series provides a FPGA based user-configurable bridge between a host processor and a custom digital interface via PCI Express. These XMC boards feature a best-in-class Artix®-7 interface to deliver the industry's lowest power and high performance.

The analog inputs monitor 20 differential or 40 single-ended channels. Software or an external hardware input can trigger A/D conversions for synchronization to external events. On-board, precision voltage references enable accurate software calibration of the module without external instruments.

The Engineering Design Kit provides users with basic info. required to develop custom FPGA firmware for download to the Xilinx® FPGA. Example FPGA design code is provided as a Vivado IP Integrator project for functions such as a one-lane PCI Express interface, DMA, digital I/O control register, and more. Users should be fluent using Xilinx Vivado® design tools.

### **Key Features & Benefits**

### FPGA Digital I/O

- Reconfigurable Xilinx FPGA

- High channel count digital interface: TTL, RS485, and LVDS interface options

- 32Mb quad serial flash memory

- 52,160 logic cells

- 65,200 Flip flops

- 2,700 kb block RAM

- 120 DSP slices

- External LVTTL clock input

- Long distance data transmission

- Example design

- Power up and system reset is failsafe

### **Analog Input**

- 20 differential or 40 single-ended inputs

- Flexible scan control

- 16-bit A/D resolution

- 8μs conversion time

- FIFO buffer with 16K sample memory

- Interrupt upon FIFIO threshold condition

- FIFO full, empty and threshold reached flags

- Programmable channel conversion control

- Programmable conversion timer

- Several scanning modes

- External trigger

### General

- Wide temperature range

- Conduction cooling options

- Software development tools for VxWorks<sup>®</sup>, Linux<sup>®</sup>, and Windows<sup>®</sup> environments

Tel 844-878-2352 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 S. Wixom Rd, Wixom, MI 48393-2417 USA

### **Performance Specifications**

### ■ XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-width module.

### ■ PCI Express Base Specification

Conforms to revision 2.0

Lanes

1 lane in each direction.

**Bus Speed**

2.5 Gbps (Generation 1).

Memory

128k space required. 1 base address register.

#### FPGA

FPGA device

Xilinx Artix-7 FPGA Model XC7A50T.

FPGA configuration

Download via flash memory.

Example FPGA program

IP integrator block diagram provided for PCIe bus 1 lane Gen 1 interface, DMA controller, on chip block RAM, flash memory and control of field I/O. See EDK kit.

### ■ I/O Processing

Field I/O Interface

PCle bus 1 lane Gen 1 interface.

I/O Connector

100 pin field I/O connector.

### Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7A50-AP323 series module (see www.acromag.com for more information).

### ■ Digital I/O

TTL Channels

48 input/output channels. Direction is controlled in groups of eight channels. 5V tolerant.

### TTL Electrical Characteristics

VIH: 2.0V minimum.

VIL: 0.8V maximum.

loн: -32.0mA.

Voн: 2.0V minimum.

Vol: 0.55V maximum at 64mA.

### Analog Input

Input configuration

20 differential or 40 single-ended.

A/D Resolution

16 bits

Input range (dip switch-selectable)

Bipolar ±5V or ±10V.

Unipolar 0 to +5V or 0 to +10V.

Data sample memory

16K sample FIFO buffer.

Maximum throughput rate

200KHz (5μS/conversion).

A/D triggers

External, and software.

System accuracy

2.4 LSB (0.014%).

Maximum overall calibrated error at 25°C.

| Input<br>Range<br>(Volts) | ADC<br>Range<br>(Volts) | Maximum<br>Error ±LSB<br>(%span) | Typical<br>Error ±LSB<br>(%span) |

|---------------------------|-------------------------|----------------------------------|----------------------------------|

| ±5                        | ±5                      | ±8.6 LSB<br>(0.013%)             | ±8.6 LSB<br>(0.013%)             |

| ±10                       | ±10                     | ±9.4 LSB<br>(0.014%)             | ±3 LSB<br>(0.005%)               |

#### Data format

Binary two's compliment and straight binary.

Input overvoltage protection

Power on: -20V to +40V. Power off: -35V to +55V

Common mode rejection ratio (60Hz)

96dB typical.

Channel-to-channel rejection ratio (60Hz)

96dB typical.

### Environmental

Operating temperature

-40 to 70°C.

Storage temperature

-55 to 100°C

Relative humidity

5 to 95% non-condensing.

### Power

| F | Power Supply | Typical | Maximum |

|---|--------------|---------|---------|

|   | +3.3V        | 455mA   | 550mA   |

|   | VPWR (+5V)   | 20mA    | 30mA    |

|   | VPWR (+12V)  | 0.7mA   | 1.4mA   |

|   | +12V         | <100mA  | 100mA   |

|   | -12V         | 0.7mA   | 1.4mA   |

### Physical

Length

5.866 inches (143.75mm.)

Width

2.9134 inches (74mm.)

Weight

3.392 oz (96.162g).

### **Ordering Information**

#### **XMC Modules**

Go to on-line ordering page >

XMC-7A51-AP323

48 TTL channels

**Custom Requirements:** Other I/O combinations are possible, contact Acromag for more information.

Build Option A: 24 EIA-485/422 channels.

Build Option B: 24 TTL and 12 EIA-485/422 channels.

Build Option C: 24 LVDS channels.

### **Accessories**

APA7-EDK

Engineering design kit. (One kit required).

5028-564

JTAG adapter cable.

#### **Carrier Cards**

See Acromag.com for a full list of XMC carrier cards.

### Software

(see software documentation for details)

APSW-API-VXW

VxWorks® software support package.

APSW-API-WIN

Windows® DLL driver software support package.

APSW-API-LNX

Linux® support (website download only).

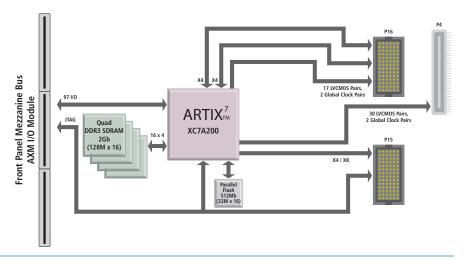

## XMC-7A200 User-Configurable Artix®-7 FPGA Modules with Plug-In I/O C€ PROHS

XMC module with PCIe interface ◆ Logic-optimized Artix-7 FPGA ◆ I/O Extension Mezzanine Modules

### **Description**

Acromag's XMC-7A modules feature a highperformance user-configurable Xilinx® Artix®-7 FPGA enhanced with high-speed memory and a high-throughput serial bus interface. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing.

Both front and rear I/O is supported. Front I/O processing is supported with plug-in AXM mezzanine cards. A variety of AXM I/O cards are available to add the flexibility of a wide range of analog and digital I/O to your design.

The rear I/O provides an 8-lane high-speed serial interface on the P16 XMC port for customerinstalled soft cores. P16 also supports 34 SelectIO channels. The P4 port adds another 60 SelectIO and global clock lines. Selectl/O signals are Artix-7 FPGA I/O pins that support single-ended I/O (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, HSTL, SSTL)

With Acromag's Artix-7 FPGA modules, you can greatly increase DSP algorithm performance for faster throughput using multiple channels and parallel hardware architectures. Free up CPU cycles by offloading algorithmic-intensive tasks to the FPGA co-processor.

These modules are ideal for high-performance customized embedded systems. Optimize your system performance by integrating highspeed programmable logic with the flexibility of software running on MicroBlaze™ soft processors.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board debugging. Additional Xilinx tools help finish your system faster. Maximize FPGA performance with Vivado® or ISE® Design Suite. And with ChipScope™ Pro tools, you can rapidly debug logic and serial interfaces

### **Key Features & Benefits**

- Reconfigurable Xilinx Artix-7 FPGA with 200k logic cells

- 128M x 64-bit DDR3 SDRAM

- 32M x 16-bit parallel flash memory for MicroBlaze FPGA program code storage

- 4-lane high-speed serial interface on rear P15 connector for PCIe Gen 1/2 (standard), Serial Rapidl/O, 10Gb Ethernet, Xilinx Aurora

- 8-lane high-speed interfaces on rear P16 connector for customer-installed soft cores

- 60 SelectI/O or 30 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P4 port

- 34 SelectI/O or 17 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P16 port

- DMA support provides data transfer between system memory and the on-board memory

- Support for Xilinx ChipScope<sup>™</sup> Pro interface

## XMC-7A200 User-Configurable Artix-7 FPGA Modules w Plug-In I/O

### **Performance Specifications**

### FPGA

### FPGA device

Xilinx® Artix®-7 FPGA.

Model XC7A200T FPGA with 215,360 logic cells and 740 DSP48E1 slices.

### FPGA configuration

Download via JTAG or flash memory.

### Example FPGA program

IP integrator block diagram provided for bus interface, front & rear I/O control, and SDRAM memory interface controller. See EDK kit.

### ■ I/O Processing

### Acromag AXM I/O Modules:

AXM modules plug into the XMC module's front mezzanine for additional I/O lines. Analog and digital I/O AXM modules are sold separately.

### Rear high-speed I/O

12 high-speed serial lanes.

x8 lanes via P15 and x8 lanes via P16.

#### Rear user I/O

P16: 17 LVDS pairs (34 LVCMOS), 2 global clock pairs. P4: 30 LVDS pairs (60 LVCMOS), 2 global clock pairs.

### ■ Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7A module (see www.acromag.com for more information).

### XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Electrical

### XMC PCIe bus interface (P15 and P16)

One 114-pin male connector (Samtec ASP-103614-05 or equivalent).

### P15 primary XMC connector

8 differential pairs (PCIe x4 standard, Serial RapidlO, 10-Gigabit Ethernet, or Xilinx Aurora). JTAG.

System Management (XMC provides hardware definition information read by an external controller using IPMI commands and I2C serial bus transactions.)

3.3V power: 4 pins at 1A/pin.

3.3V auxiliary power: 1 pin, powers volatile memory to store the bitstream encryption key.

Variable power (5V or 12V): 8 pins at 1A per pin.

### P16 XMC connector

8 differential pairs (PCIe, Serial RapidIO, or Xilinx Aurora).

17 LVDS pairs or 34 SelectI/O signals (differential pairs grouped per VITA 46.0 X38s).

### 2 global clock pairs.

Vcco pins are powered by 2.5V and support the 2.5V VO standards.

#### P4 PMC rear I/O connector

64-pin female receptacle header (AMP 120527-1 or equivalent).

64 I/O connections (30 LVDS pairs plus two global clocks).

Vcco pins powered by 2.5V and support the 2.5V I/O standards

### Environmental

### Operating temperature

XMC-7A200-LF: -40 to 55°C.

### Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

#### Power

+12 Volts 0.1 mA typical

#### **MTBF**

Contact the factory.

### **Ordering Information**

NOTE: XMC-7KA-EDK is required to configure FPGA.

### XMC Modules

#### XMC-7A200-LF

User-configurable Artix-7 FPGA, 200k logic cells with AXM support

### Accessories

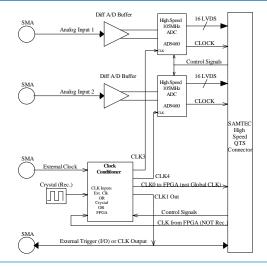

### AXM-A75

16 analog inputs, 8 analog outputs, and 16 digital I/O

### AXM-A30

2 analog input 100MHz 16-bit A/D channels.

#### AXM-D02

30 RS485 differential I/O channels.

### AXM-D03

16 CMOS and 22 RS485 differential I/O channels.

### AXM-D04

30 LVDS I/O channels.

### AXM-??

Custom I/O configurations available, call factory

### Software

For more information, see www.acromag.com.

#### XMC-7KA-EDK

Engineering Design Kit (one kit required)

### PMCSW-API-VXW

VxWorks® 32-bit software support package

#### **PCISW-API-WIN**

Windows® DLL software support package

### PCISW-API-LNX

Linux® support (website download only)

XMC-7A200-LF with AXM-A75 and heat sink.

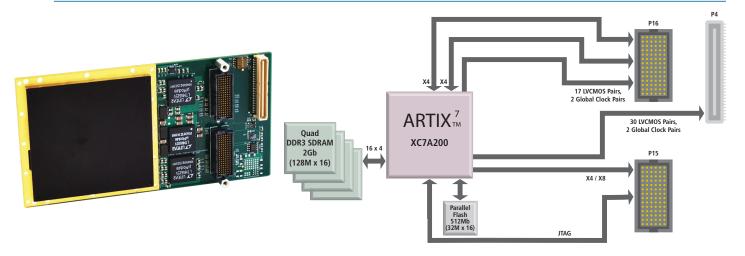

## XMC-7A200 CC User-Configurable Conduction-Cooled Artix®-7 FPGA Modules C€ ® RoHS

XMC module with PCIe interface ◆ Logic-optimized Artix-7 FPGA ◆ Conduction-Cooled

### **Description**

Acromag's XMC-7A200CC modules feature a high-performance user-configurable Xilinx® Artix®-7 FPGA enhanced with high-speed memory and a high-throughput serial bus interface. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing.

The rear I/O provides an 8-lane high-speed serial interface on the P16 XMC port for customer-installed soft cores. P16 also supports 34 SelectIO channels. The P4 port adds another 60 SelectIO and global clock lines. SelectI/O signals are Artix-7 FPGA I/O pins that support single-ended I/O (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, HSTL, SSTL)

With Acromag's Artix-7 FPGA modules, you can greatly increase DSP algorithm performance for faster throughput using multiple channels and parallel hardware architectures. Free up CPU cycles by offloading algorithmic-intensive tasks to the FPGA co-processor.

These modules are ideal for high-performance customized embedded systems. Optimize your system performance by integrating high-speed programmable logic with the flexibility of software running on MicroBlaze<sup>™</sup> soft processors.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board debugging. Additional Xilinx tools help finish your system faster. Maximize FPGA performance with Vivado® or ISE® Design Suite. And with ChipScope™ Pro tools, you can rapidly debug logic and serial interfaces

### **Key Features & Benefits**

- Reconfigurable Xilinx Artix-7 FPGA with 215K logic cells

- 128M x 64-bit DDR3 SDRAM

- 32M x 16-bit parallel flash memory for MicroBlaze FPGA program code storage

- 4-lane high-speed serial interface on rear P15 connector for PCle Gen 1/2 (standard), Serial Rapidl/O, 10Gb Ethernet, Xilinx Aurora

- 8-lane high-speed interfaces on rear P16 connector for customer-installed soft cores

- 60 Selectl/O or 30 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P4 port

- 34 Selectl/O or 17 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P16 port

- DMA support provides data transfer between system memory and the on-board memory

- Support for Xilinx ChipScope<sup>™</sup> Pro interface

- Extended temperature conduction-cooled

## XMC-7A200 CC User-Configurable Conduction-Cooled Artix-7 FPGA Modules

### **Performance Specifications**

### FPGA

### FPGA device

Xilinx Artix-7 FPGA

Model XC7A200T FPGA with 215,360 logic cells and 740 DSP48E1 slices.

### FPGA configuration

Download via JTAG or flash memory.

### Example FPGA program

IP integrator block diagram provided for bus interface, front & rear I/O control, and SDRAM memory interface controller. See EDK kit.

### I/O Processing

### Rear high-speed I/O

12 high-speed serial lanes.

x4 lanes via P15 and x8 lanes via P16.

#### Rear user I/O

P16: 17 LVDS pairs (34 LVCMOS), 2 global clock pairs. P4: 30 LVDS pairs (60 LVCMOS), 2 global clock pairs.

### ■ Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7 series module (see www.acromag.com for more information).

### XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Electrical

### XMC PCIe bus interface (P15 and P16)

One 114-pin male connector (Samtec ASP-103614-05 or equivalent).

### P15 primary XMC connector

4 differential pairs (PCIe standard, Serial RapidIO, 10-Gigabit Ethernet, or Xilinx Aurora). JTAG.

System Management (XMC provides hardware definition information read by an external controller using IPMI commands and I2C serial bus transactions.)

3.3V power: 4 pins at 1A/pin.

3.3V auxiliary power: 1 pin, powers volatile memory to store the bitstream encryption key.

Variable power (5V or 12V): 8 pins at 1A per pin.

### P16 XMC connector

8 differential pairs (PCIe, Serial RapidIO, or Xilinx Aurora).

17 LVDS pairs or 34 Selectl/O signals (differential pairs grouped per VITA 46.0 X38s).

2 global clock pairs.

Vcco pins are powered by 2.5V and support the 2.5V VO standards.

### P4 PMC rear I/O connector

64-pin female receptacle header (AMP 120527-1 or equivalent).

64 I/O connections (30 LVDS pairs plus two global clocks).

Vcco pins powered by 2.5V and support the 2.5V I/O standards

### Environmental

### Operating temperature

XMC-7A200CC-LF: Conduction-cooled, -40 to 75°C.

#### Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

### Power

3.3V (±5%): 7W typical. 12V (±5%): 2W typical. 3.3V AUX (±5%): 57µW

### MTBF

Contact the factory.

### **Ordering Information**

NOTE: XMC-7KA-EDK is required to configure FPGA.

### XMC Modules

#### Go to on-line ordering page >

### XMC-7A200CC-LF

User-configurable Artix-7 FPGA, 215k logic cells, conduction-cooled

#### Software

For more information, see www.acromag.com.

#### XMC-7KA-EDK

Engineering Design Kit (one kit required)

#### PMCSW-API-VXW

VxWorks® 32-bit software support package

#### PCISW-API-WIN

Windows® DLL software support package

#### PCISW-API-LNX

Linux® support (website download only)

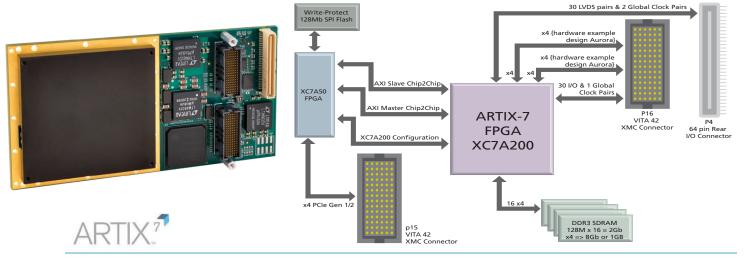

## **XMC-7AWP** User-Configurable Artix®-7 FPGA Modules

XMC module with PCIe interface ◆ Logic-optimized Artix-7 FPGA ◆ Write-protected flash

### **Description**

Acromag's XMC-7AWP modules feature a high-performance user-configurable Xilinx® Artix®-7 FPGA enhanced with high-speed memory and a high-throughput serial bus interface. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing.

For security, the FPGA's configuration flash is write-protected. The XC7A200 is only configurable via PCIe bus or JTAG. There is no configuration memory.

The rear I/O provides an 8-lane high-speed serial interface on the P16 XMC port for customer-installed soft cores. P16 also supports 34 SelectIO channels. The P4 port adds another 60 SelectIO and global clock lines. SelectIO signals are Artix-7 FPGA I/O pins that support single-ended I/O (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, HSTL, SSTL)

With Acromag's Artix-7 FPGA modules, you can greatly increase DSP algorithm performance for faster throughput using multiple channels and parallel hardware architectures. Free up CPU cycles by offloading algorithmic-intensive tasks to the FPGA co-processor.

These modules are ideal for high-performance customized embedded systems. Optimize your system performance by integrating high-speed programmable logic with the flexibility of software running on MicroBlaze™ soft processors.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board debugging. Additional Xilinx tools help finish your system faster. Maximize FPGA performance with Vivado® or ISE® Design Suite. And with Integrated Logic Analyzer, you can rapidly debug logic and serial interfaces.

### **Key Features & Benefits**

- Reconfigurable Xilinx Artix-7 FPGA with 200k logic cells

- 128M x 64-bit DDR3 SDRAM

- XC7A50 FPGA bitstream storage flash is write protected via DIP switch selection.

- 4-lane high-speed serial interface on rear P15 connector for PCle Gen 1/2 (standard), Serial Rapidl/O, 10Gb Ethernet, Xilinx Aurora

- 8-lane high-speed interfaces on rear P16 connector for customer-installed soft cores

- 60 SelectIO or 30 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P4 port

- 34 SelectIO or 17 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P16 port

- DMA support provides data transfer between system memory and the on-board memory

## **XMC-7AWP** User-Configurable Artix-7 FPGA Modules

### **Performance Specifications**

### FPGA

### FPGA device

Xilinxo Artix®-7 FPGA.

Model XC7A200T FPGA with 215,360 logic cells and 740 DSP48E1 slices.

### FPGA configuration

XC7A200 is configurable via PCle bus or JTAG. XC7A50 is configured from flash memory or JTAG. Flash is write protected by default.

### Example FPGA program

IP integrator block diagram provided for bus interface, front & rear I/O control, and SDRAM memory interface controller. See EDK kit.

### I/O Processing

#### Rear high-speed I/O

12 high-speed serial lanes.

x8 lanes via P15 and x8 lanes via P16.

#### Rear user I/O

P16: 17 LVDS pairs (34 LVCMOS), 2 global clock pairs. P4: 30 LVDS pairs (60 LVCMOS), 2 global clock pairs.

### ■ Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7AWP module (see www.acromag.com for more information).

### XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Electrical

### XMC PCIe bus interface (P15 and P16)

One 114-pin male connector (Samtec ASP-103614-05 or equivalent).

### P15 primary XMC connector

8 differential pairs (PCIe x4 standard, Serial RapidIO, 10-Gigabit Ethernet, or Xilinx Aurora). JTAG.

System Management (XMC provides hardware definition information read by an external controller using IPMI commands and I2C serial bus transactions.)

3.3V power: 4 pins at 1A/pin.

3.3V auxiliary power: 1 pin, powers volatile memory to store the bitstream encryption key.

Variable power (5V or 12V): 8 pins at 1A per pin.

### P16 XMC connector

8 differential pairs (PCIe, Serial RapidIO, or Xilinx Aurora).

17 LVDS pairs or 34 Selectl/O signals (differential pairs grouped per VITA 46.0 X38s).

2 global clock pairs.

Vcco pins are powered by 2.5V and support the 2.5V VO standards.

### P4 PMC rear I/O connector

64-pin female receptacle header (AMP 120527-1 or equivalent).

64 I/O connections (30 LVDS pairs plus two global clocks).

FPGA Vcco pins powered by 2.5V and support 2.5V VO standards. Optionally can be powered by 3.3V to support 3.3V VO standards.

#### Environmental

### Operating temperature

XMC-7AWP: -40 to 75°C cold-plate.

### Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

#### Power

+3.3 Volts 2.1 A typical +3.3 Aux Volts 17 uA typical

+12/5 Volts (VPWR) 150 mA @ +12V typical

+12 Volts 0.1 mA typical

#### **MTBF**

Contact the factory.

### **Ordering Information**

NOTE: XMC-7AWP-EDK is required to configure FPGA.

### XMC Modules

Go to on-line ordering page >

### XMC-7AWP

User-configurable Artix-7 FPGA, 200k logic cells

#### Software

#### XMC-7AWP-EDK

Engineering Design Kit (one kit required)

### PMCSW-API-VXW

VxWorks® 32-bit software support package

### PCISW-API-WIN

Windows® DLL software support package

### PCISW-API-LNX

Linux® support (website download only)

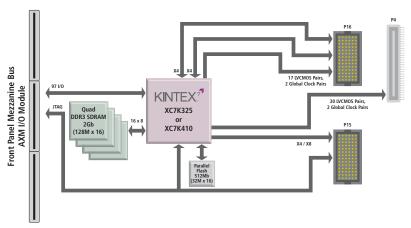

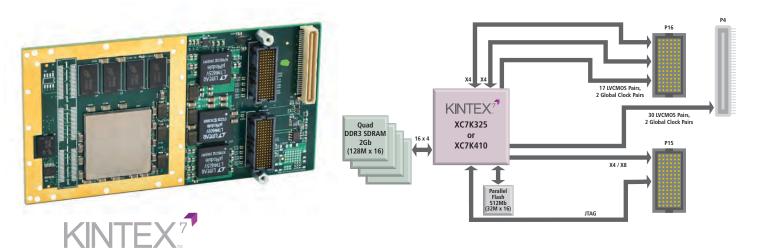

## XMC-7K AX User-Configurable Kintex-7 FPGA Modules with Plug-In I/O

XMC module with PCIe interface ◆ Logic-optimized Kintex-7 FPGA ◆ I/O Extension Mezzanine Modules

### **Description**

Acromag's <u>XMC-7K</u> modules feature a high-performance user-configurable Xilinx® Kintex®-7 FPGA enhanced with high-speed memory and a high-throughput serial bus interface. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing.

Both front and rear I/O is supported. Front I/O processing is supported with plug-in AXM mezzanine cards. A variety of AXM I/O cards are available to add the flexibility of a wide range of analog and digital I/O to your design.

The rear I/O provides an 8-lane high-speed serial interface on the P16 XMC port for customer-installed soft cores. P16 also supports 34 SelectIO channels. The P4 port adds another 60 SelectIO and global clock lines. SelectI/O signals are Kintex-7 FPGA I/O pins that support single-ended I/O (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, HSTL, SSTL)

Two versions of the Kintex-7 are available, offering a choice of an FPGA device with 325k or 410k logic cells.

With Acromag's Kintex-7 FPGA modules, you can greatly increase DSP algorithm performance for faster throughput using multiple channels and parallel hardware architectures. Free up CPU cycles by offloading algorithmic-intensive tasks to the FPGA co-processor.

These modules are ideal for high-performance customized embedded systems. Optimize your system performance by integrating high-speed programmable logic with the flexibility of software running on MicroBlaze<sup>™</sup> soft processors.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board debugging. Additional Xilinx tools help finish your system faster. Maximize FPGA performance with Vivado® or ISE® Design Suite. And with ChipScope™ Pro tools, you can rapidly debug logic and serial interfaces

### **Key Features & Benefits**

- Reconfigurable Xilinx Kintex-7 FPGA with 325k or 410k logic cells

- 128M x 128-bit DDR3 SDRAM

- 32M x 16-bit parallel flash memory for MicroBlaze FPGA program code storage

- 8-lane high-speed serial interface on rear P15 connector for PCle Gen 1/2 (standard), Serial Rapidl/O, 10Gb Ethernet, Xilinx Aurora

- 8-lane high-speed interfaces on rear P16 connector for customer-installed soft cores

- 60 SelectI/O or 30 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P4 port

- 34 SelectI/O or 17 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P16 port

- DMA support provides data transfer between system memory and the on-board memory

- Support for Xilinx ChipScope<sup>™</sup> Pro interface

## XMC-7K AX User-Configurable Kintex-7 FPGA Modules w Plug-In I/O

### **Performance Specifications**

### FPGA

### FPGA device

Xilinx Kintex-7 FPGA.

Model XC7K325T FPGA with 326,080 logic cells and 840 DSP48E1 slices or Model XC7K410T with 406,720 logic cells and 1540 DSP48E1 slices.

### FPGA configuration

Download via JTAG or flash memory.

### Example FPGA program

IP integrator block diagram provided for bus interface, front & rear I/O control, and SDRAM memory interface controller. See EDK kit.

### I/O Processing

### Acromag AXM I/O Modules:

AXM modules plug into the XMC module's front mezzanine for additional I/O lines. Analog and digital I/O AXM modules are sold separately.

### Rear high-speed I/O

12 high-speed serial lanes.

### x8 lanes via P15 and x4 lanes via P16.

#### Rear user I/O

P16: 17 LVDS pairs (34 LVCMOS), 2 global clock pairs. P4: 30 LVDS pairs (60 LVCMOS), 2 global clock pairs.

### ■ Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7K module (see www.acromag.com for more information).

### XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Electrical

### XMC PCIe bus interface (P15 and P16)

One 114-pin male connector (Samtec ASP-103614-05 or equivalent).

### P15 primary XMC connector

8 differential pairs (PCIe standard, Serial RapidIO, 10-Gigabit Ethernet, or Xilinx Aurora). JTAG.

System Management (XMC provides hardware definition information read by an external controller using IPMI commands and I2C serial bus transactions.)

3.3V power: 4 pins at 1A/pin.

3.3V auxiliary power: 1 pin, powers volatile memory to store the bitstream encryption key.

Variable power (5V or 12V): 8 pins at 1A per pin.

#### P16 XMC connector

4 differential pairs (PCIe, Serial RapidIO, or Xilinx Aurora).

17 LVDS pairs or 34 Selectl/O signals (differential pairs grouped per VITA 46.0 X38s).

### 2 global clock pairs.

Vcco pins are powered by 2.5V and support the 2.5V I/O standards.

### P4 PMC rear I/O connector

64-pin female receptacle header (AMP 120527-1 or equivalent).

64 I/O connections (30 LVDS pairs plus two global clocks).

Vcco pins powered by 2.5V and support the 2.5V I/O standards.

### Environmental

### Operating temperature

XMC-7K325AX-LF: -40 to 45°C. XMC-7K410AX-LF: -40 to 40°C

### Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

#### Power

3.3V (±5%): 7.8W typical. 12V (±5%): 2.7W typical 3.3V AUX (±5%): 57μW

#### MTBF

Contact the factory.

### **Ordering Information**

NOTE: XMC-7K-EDK is required to configure FPGA.

### XMC Modules

#### XMC-7K325AX-LF

User-configurable Kintex-7 FPGA, 325k logic cells with AXM support

### XMC-7K410AX-LF

User-configurable Kintex-7 FPGA, 410k logic cells with AXM support

#### Accessories

#### AXM-A75

16 analog inputs, 8 analog outputs, and 16 digital I/O

### AXM-A30

2 analog input 100MHz 16-bit A/D channels.

#### AXM-D02

30 RS485 differential I/O channels.

#### AXM-D03

16 CMOS and 22 RS485 differential I/O channels.

#### AXM-D04

30 LVDS I/O channels.

#### AXM-??

Custom I/O configurations available, call factory.

### Software

#### XMC-7KA-EDK

Engineering Design Kit (one kit required)

### PMCSW-API-VXW

VxWorks® 32-bit software support package

### PCISW-API-WIN

Windows® DLL software support package

#### PCISW-API-LNX

Linux<sup>™</sup> support (website download only)

XMC-7K325AX-LF shown with optional AXM-A75

##

XMC module with PCIe interface ◆ Logic-optimized Kintex-7 FPGA ◆ Conduction-Cooled

### **Description**

Acromag's XMC-7K modules feature a high-performance user-configurable Xilinx® Kintex®-7 FPGA enhanced with high-speed memory and a high-throughput serial bus interface. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing.

The rear I/O provides an 8-lane high-speed serial interface on the P16 XMC port for customer-installed soft cores. P16 also supports 34 SelectIO channels. The P4 port adds another 60 SelectIO and global clock lines. SelectI/O signals are Kintex-7 FPGA I/O pins that support single-ended I/O (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, HSTL, SSTL)

Two versions of the Kintex-7 are available, offering a choice of an FPGA device with 325k or 410k logic cells.

With Acromag's Kintex-7 FPGA modules, you can greatly increase DSP algorithm performance for faster throughput using multiple channels and parallel hardware architectures. Free up CPU cycles by offloading algorithmic-intensive tasks to the FPGA co-processor.

These modules are ideal for high-performance customized embedded systems. Optimize your system performance by integrating high-speed programmable logic with the flexibility of software running on MicroBlaze<sup>™</sup> soft processors.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board debugging. Additional Xilinx tools help finish your system faster. Maximize FPGA performance with Vivado® or ISE® Design Suite. And with ChipScope™ Pro tools, you can rapidly debug logic and serial interfaces

### **Key Features & Benefits**

- Reconfigurable Xilinx Kintex-7 FPGA with 325k or 410k logic cells

- 128M x 64-bit DDR3 SDRAM

- 32M x 16-bit parallel flash memory for MicroBlaze FPGA program code storage

- 8-lane high-speed serial interface on rear P15 connector for PCle Gen 1/2 (standard), Serial Rapidl/O, 10Gb Ethernet, Xilinx Aurora

- 8-lane high-speed interfaces on rear P16 connector for customer-installed soft cores

- 60 Selectl/O or 30 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P4 port

- 34 Selectl/O or 17 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P16 port

- DMA support provides data transfer between system memory and the on-board memory

- Support for Xilinx ChipScope<sup>™</sup> Pro interface

- Extended temperature conduction-cooled

## XMC-7K CC User-Configurable Conduction-Cooled Kintex-7 FPGA Modules

### **Performance Specifications**

### FPGA

#### FPGA device

Xilinx Kintex-7 FPGA.

Model XC7K325T FPGA with 326,080 logic cells and 840 DSP48E1 slices or Model XC7K410T with 406,720 logic cells and 1540 DSP48E1 slices.

### FPGA configuration

Download via JTAG or flash memory.

### Example FPGA program

IP integrator block diagram provided for bus interface, front & rear I/O control, and SDRAM memory interface controller. See EDK kit.

### I/O Processing

### Rear high-speed I/O

16 high-speed serial lanes.

x8 lanes via P15 and x8 lanes via P16.

#### Rear user I/O

P16: 17 LVDS pairs (34 LVCMOS), 2 global clock pairs. P4: 30 LVDS pairs (60 LVCMOS), 2 global clock pairs.

### ■ Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7K module (see www.acromag.com for more information).

#### XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Electrical

### XMC PCIe bus interface (P15 and P16)

One 114-pin male connector (Samtec ASP-103614-05 or equivalent).

### P15 primary XMC connector

8 differential pairs (PCIe standard, Serial RapidIO, 10-Gigabit Ethernet, or Xilinx Aurora). JTAG.

System Management (XMC provides hardware definition information read by an external controller using IPMI commands and I2C serial bus transactions.)

3.3V power: 4 pins at 1A/pin.

3.3V auxiliary power: 1 pin, powers volatile memory to store the bitstream encryption key.

Variable power (5V or 12V): 8 pins at 1A per pin.

#### P16 XMC connector

4 differential pairs (PCIe, Serial RapidIO, or Xilinx Aurora)

17 LVDS pairs or 34 Selectl/O signals (differential pairs grouped per VITA 46.0 X38s).

2 global clock pairs.

Vcco pins are powered by 2.5V and support the 2.5V I/O standards.

### P4 PMC rear I/O connector

64-pin female receptacle header (AMP 120527-1 or equivalent).

64 I/O connections (30 LVDS pairs plus two global clocks)

Vcco pins powered by 2.5V and support the 2.5V I/O standards.

### Environmental

### Operating temperature

XMC-7K325AX-LF: Conduction-cooled, -40 to 70°C. XMC-7K410AX-LF: Conduction-cooled, -40 to 70°C

### Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

#### Power

3.3V (±5%): 7.8W typical. 12V (±5%): 2.7W typical. 3.3V AUX (±5%): 57μW

#### MTBF

Contact the factory.

### **Ordering Information**

NOTE: XMC-7K-EDK is required to configure FPGA.

#### XMC Modules

### XMC-7K325CC-LF

User-configurable Kintex-7 FPGA, 325k logic cells, conduction-cooled

#### XMC-7K410CC-LF

User-configurable Kintex-7 FPGA, 410k logic cells, conduction-cooled

### Software

#### XMC-7KA-EDK

Engineering Design Kit (one kit required)

### PMCSW-API-VXW

VxWorks® 32-bit software support package

### **PCISW-API-WIN**

Windows® DLL software support package

### PCISW-API-LNX

Linux<sup>™</sup> support (website download only)

XMC-7K325CC-LF shown with heatsink

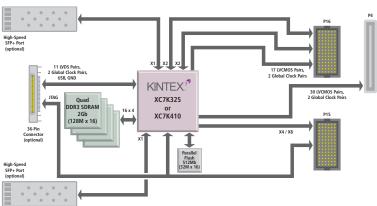

#### User-Configurable Kintex-7 FPGA Modules with Dual SFP+ Ports CE A ORDINATION OF THE STATE OF THE XMC-7K F

XMC module with PCIe and SFP+/Aurora interface ◆ Logic-optimized Kintex-7 FPGA ◆ 10-Gigabit Ethernet

### **Description**

Acromag's XMC-7K modules feature a highperformance user-configurable Xilinx® Kintex®-7 FPGA enhanced with high-speed memory and a high-throughput serial interface. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing.

Two versions of this module are available, offering a choice of an FPGA device with 325k or 410k logic cells.

Front I/O adds dual SFP+ ports and a VHDCR connector. The two SFP+ ports each provide a copper or fibre interface of up to 10.3125Gbps. They also support a Gigabit Ethernet interface. The VHDCR connector interfaces JTAG, USB, and 22 SelectIO.

The rear I/O provides an 4-lane high-speed serial interface on the P16 XMC port for customerinstalled soft cores. P16 also supports 34 SelectIO channels. The P4 port adds another 60 SelectIO and global clock lines. SelectI/O signals are Kintex-7 FPGA I/O pins that support single-ended I/O (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, HSTL, SSTL).

With Acromag's Kintex-7 FPGA modules, you can greatly increase DSP algorithm performance for faster throughput using multiple channels and parallel hardware architectures. Free up CPU cycles by offloading algorithmic-intensive tasks to the FPGA co-processor.

These modules are ideal for high-performance customized embedded systems. Optimize your system performance by integrating highspeed programmable logic with the flexibility of software running on MicroBlaze™ soft processors.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board debugging. Additional Xilinx tools help finish your system faster. Maximize FPGA performance with Vivado® or ISE® Design Suite. And with ChipScope™ Pro tools, you can rapidly debug logic and serial interfaces

### **Key Features & Benefits**

- Reconfigurable Xilinx Kintex-7 FPGA with 325k or 410k logic cells

- 128M x 64-bit DDR3 SDRAM

- 32M x 16-bit parallel flash memory for MicroBlaze FPGA program code storage

- 8-lane high-speed serial interface on rear P15 connector for PCIe Gen 1/2 (standard), Serial Rapidl/O, 10Gb Ethernet, Xilinx Aurora

- 4-lane high-speed interfaces on rear P16 connector for customer-installed soft cores

- Dual SFP+ ports for Fibre Channel or 10GbE

- 60 SelectI/O or 30 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P4 port

- 34 SelectI/O or 17 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P16 port

- 22 SelectI/O, 2 global clock pairs, JTAG, USB, and ground signals via front 36-pin connector

- DMA support provides data transfer between system memory and the on-board memory

- Support for Xilinx ChipScope™ Pro interface

Tel 248-295-0310 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 Wixom Rd, Wixom, MI 48393 USA

## XMC-7K F User-Configurable Kintex-7 FPGA Modules w Dual SFP+ Ports

### **Performance Specifications**

### FPGA

### FPGA device

Xilinx Kintex-7 FPGA.

Model XC7K325T FPGA with 326,080 logic cells and 840 DSP48E1 slices or Model XC7K410T with 406,720 logic cells and 1540 DSP48E1 slices.

### FPGA configuration

Download via JTAG or flash memory.

### Example FPGA program

IP integrator block diagram provided for bus interface, front & rear I/O control, and SDRAM memory interface controller. See EDK kit.

### ■ I/O Processing

### Front high-speed I/O

Two x1 lanes via SFP+ connectors for Gigabit Ethernet and Fibre Channel interface

#### Front user I/O

36-pin connector provides JTAG connection, USB signals, 2 global differential clock pairs, 11 LVDS signal pairs, and 2 ground signals.

### Rear high-speed I/O

12 high-speed serial lanes.

x8 lanes via P15 and x4 lanes via P16.

#### Rear user I/O

P16: 17 LVDS pairs (34 LVCMOS), 2 global clock pairs. P4: 30 LVDS pairs (60 LVCMOS), 2 global clock pairs.

### Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7K module (see www.acromag.com for more information).

### XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Electrical

### XMC PCIe bus interface (P15 and P16)

One 114-pin male connector (Samtec ASP-103614-05 or equivalent).

### P15 primary XMC connector

8 differential pairs (PCIe standard, Serial RapidIO, 10-Gigabit Ethernet, or Xilinx Aurora). JTAG.

System Management (XMC provides hardware definition information read by an external controller using IPMI commands and I2C serial bus transactions.)

3.3V power: 4 pins at 1A/pin.

3.3V auxiliary power: 1 pin for system management. Variable power (5V or 12V): 8 pins at 1A per pin.

#### P16 XMC connector

4 differential pairs (PCle, Serial RapidlO, or Xilinx Aurora).

17 LVDS pairs or 34 Selectl/O signals (differential pairs grouped per VITA 46.0 X38s).

2 global clock pairs.

Vcco pins are powered by 2.5V and support the 2.5V I/O standards.

### P4 PMC rear I/O connector

64-pin female receptacle header (AMP 120527-1 or equivalent).

64 I/O connections (30 LVDS pairs plus two global clocks).

Vcco pins powered by 2.5V and support the 2.5V I/O standards.

#### VHDCR connector

36-position connector (Samtec VHDCR-36-01-M-RA) mates with industry-standard VHDCI cable assemblies.

### SFP+ host connector

SFP transceiver signals route directly to Kintex-7 FPGA. 10.3125Gb/S maximum data rate.

SFP+ copper (Gigabit Ethernet) or fibre optic modules available from Acromag.

### **Ordering Information**

NOTE: XMC-7K-EDK is required to configure FPGA.

### XMC Modules

#### XMC-7K325F-LF

User-configurable Kintex-7 FPGA, 325k logic cells plus SFP front I/O

### XMC-7K410F-LF

User-configurable Kintex-7 FPGA, 410k logic cells plus SFP front I/O

#### Accessories

### 5025-921

Cable, VHDCI 36-pin to SCSI-2, 6 feet long.

#### 5028-449

Cable, copper twin-ax, SFP to SFP, 1 meter long.

#### 5028-455

Transceiver, 10/100/1000BASE-T copper SFP, up to 1.25Gb/s bi-directional data links.

#### 5028-452

Transceiver, short-wavelength SFP, up to 2.125Gb/s bi-directional data links.

### Software

#### XMC-7KA-EDK

Engineering Design Kit (one kit required)

### PMCSW-API-VXW

VxWorks® 32-bit software support package

#### **PCISW-API-WIN**

Windows® DLL software support package

### **PCISW-API-LNX**

Linux® support (website download only)

### **■** Environmental

### Operating temperature

XMC-7K325F-LF: -40 to 55°C. XMC-7K410F-LF: -40 to 55°C.

### Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

### Power

3.3V (±5%): 7.8W typical. 12V (±5%): 2.7W typical. 3.3V AUX (±5%): 57μW typical.

#### MTBF

Contact the factory.

XMC-7K325F-LF shown with heatsink

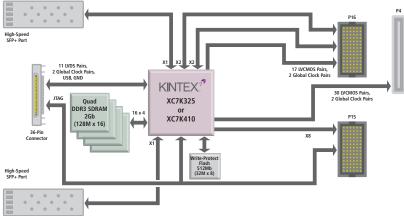

## XMC-7KWP User-Configurable Kintex-7 FPGA Modules with Dual SFP+ Ports

XMC module ◆ Kintex-7 FPGA ◆ 10-Gigabit Ethernet ◆ Write-protected flash

### **Description**

Acromag's XMC-7KWP modules feature a high-performance user-configurable Xilinx® Kintex®-7 FPGA enhanced with high-speed memory and a high-throughput serial interface. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing. For security, the FPGA's configuration flash is write-protected.

Two versions of this module are available, offering a choice of an FPGA device with 325k or 410k logic cells.

Front I/O adds dual SFP+ ports and a VHDCR connector. The two SFP+ ports each provide a copper or fibre interface of up to 10.3125Gbps. They also support a Gigabit Ethernet interface. The VHDCR connector interfaces JTAG, USB, and 22 SelectIO.

The rear I/O provides 4-lane high-speed serial interface on the P16 XMC port for customer-installed soft cores. P16 also supports 34 SelectIO channels. The P4 port adds another 60 SelectIO and global clock lines. SelectIO signals are Kintex-7 FPGA I/O pins that support single-ended I/O (LVCMOS, HSTL, SSTL) and differential I/O standards (LVDS, HT, LVPECL, BLVDS, HSTL, SSTL).

With Acromag's Kintex-7 FPGA modules, you can greatly increase DSP algorithm performance for faster throughput using multiple channels and parallel hardware architectures. Free up CPU cycles by offloading algorithmic-intensive tasks to the FPGA co-processor.

These modules are ideal for high-performance customized embedded systems. Optimize your system performance by integrating high-speed programmable logic with the flexibility of software running on MicroBlaze™ soft processors.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board debugging. Additional Xilinx tools help finish your system faster. Maximize FPGA performance with Vivado® or ISE® Design Suite. And with ChipScope™ Pro tools, you can rapidly debug logic and serial interfaces.

### **Key Features & Benefits**

- Reconfigurable Xilinx Kintex-7 FPGA with 325k or 410k logic cells

- 128M x 64-bit DDR3 SDRAM

- 32M x 16-bit parallel flash memory for MicroBlaze FPGA program code storage

- FPGA bitstream storage flash write-protected unless access jumper installed

- 8-lane high-speed serial interface on rear P15 connector for PCle Gen 1/2 (standard), Serial Rapidl/O, 10Gb Ethernet, Xilinx Aurora

- 4-lane high-speed interfaces on rear P16 connector for customer-installed soft cores

- Dual SFP+ ports for Fibre Channel or 10GbE

- 60 SelectIO or 30 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P4 port

- 34 SelectIO or 17 LVDS pairs plus 2 global clock pairs direct to FPGA via rear P16 port

- 22 SelectIO, 2 global clock pairs, JTAG, USB, and ground signals via front 36-pin connector

- DMA support provides data transfer between system memory and the on-board memory

- Support for Xilinx ChipScope<sup>™</sup> Pro interface

Tel 844-878-2352 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 Wixom Rd, Wixom, MI 48393 USA

## XMC-7KWP User-Configurable Kintex-7 FPGA Modules w Dual SFP+ Ports

### **Performance Specifications**

### FPGA

### FPGA device

Xilinx Kintex-7 FPGA

Model XC7K325T FPGA with 326,080 logic cells and 840 DSP48E1 slices or Model XC7K410T with 406,720 logic cells and 1540 DSP48E1 slices.

### FPGA configuration

Download via JTAG or flash memory. Installation of 2mm pitch jumper shunt required for writing to flash memory.

### Example FPGA program

IP integrator block diagram provided for bus interface, front & rear I/O control, and SDRAM memory interface controller. See EDK kit.

### ■ I/O Processing

### Front high-speed I/O

Two x1 lanes via SFP+ connectors for Gigabit Ethernet and Fibre Channel interface.

#### Front user I/O

36-pin connector provides JTAG connection, USB signals, 2 global differential clock pairs, 11 LVDS signal pairs, and 2 ground signals.

### Rear high-speed I/O

12 high-speed serial lanes.

x8 lanes via P15 and x4 lanes via P16.

#### Rear user I/O

P16: 17 LVDS pairs (34 LVCMOS), 2 global clock pairs. P4: 30 LVDS pairs (60 LVCMOS), 2 global clock pairs.

### ■ Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-7K module (see www.acromag.com for more information).

### XMC Compliance

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Electrical

### XMC PCIe bus interface (P15 and P16)

One 114-pin male connector (Samtec ASP-103614-05 or equivalent).

### P15 primary XMC connector

8 differential pairs (PCIe standard, Serial RapidIO, 10-Gigabit Ethernet, or Xilinx Aurora). JTAG.

System Management (XMC provides hardware definition information read by an external controller using IPMI commands and I2C serial bus transactions.)

3.3V power: 4 pins at 1A/pin.

3.3V auxiliary power: 1 pin for system management. Variable power (5V or 12V): 8 pins at 1A per pin.

### P16 XMC connector

4 differential pairs (PCIe, Serial RapidIO, or Xilinx Aurora).

17 LVDS pairs or 34 SelectI/O signals (differential pairs grouped per VITA 46.0 X38s).

2 global clock pairs.

Vcco pins are powered by 2.5V and support the 2.5V I/O standards.

#### P4 PMC rear I/O connector

64-pin female receptacle header

(AMP 120527-1 or equivalent).

64 I/O connections (30 LVDS pairs plus two global clocks).

Vcco pins powered by 2.5V and support the 2.5V I/O standards.

#### VHDCR connector

36-position connector (Samtec VHDCR-36-01-M-RA) mates with industry-standard VHDCI cable assemblies.

### SFP+ host connector

SFP transceiver signals route directly to Kintex-7 FPGA. 10.3125Gb/S maximum data rate.

SFP+ copper (Gigabit Ethernet) or fibre optic modules available from Acromag.

### JTAG voltage level

2.5V default.

Resistor stuff option for 3.3V (consult factory).

### Environmental

### Operating temperature

XMC-7KWP-325F: -40 to 55°C. XMC-7KWP-410F: -40 to 55°C.

### Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

#### Power

3.3V (±5%): 7.8W typical. 12V (±5%): 2.7W typical. 3.3V AUX (±5%): 57µW typical.

### MTBF

Contact the factory.

### **Ordering Information**

NOTE: XMC-7KA-EDK is required to configure FPGA.

### XMC Modules

Go to on-line ordering page >

### XMC-7KWP-325F

User-configurable Kintex-7 FPGA, 325k logic cells plus SFP front I/O, write protected flash

#### XMC-7KWP-410F

User-configurable Kintex-7 FPGA, 410k logic cells plus SFP front I/O, write protected flash

#### Accessories

#### 5025-921

Cable, VHDCI 36-pin to SCSI-2, 6 feet long.

#### 5028-449

Cable, copper twin-ax, SFP to SFP, 1 meter long.

#### 5028-455

Transceiver, 10/100/1000BASE-T copper SFP, up to 1.25Gb/s bi-directional data links.

#### 5028-452

Transceiver, short-wavelength SFP, up to 2.125Gb/s bi-directional data links.

### Software

#### XMC-7KA-EDK

Engineering Design Kit (one kit required)

### PMCSW-API-VXW

VxWorks® 32-bit software support package

### PCISW-API-WIN

Windows® DLL software support package

#### PCISW-API-LNX

Linux® support (website download only)

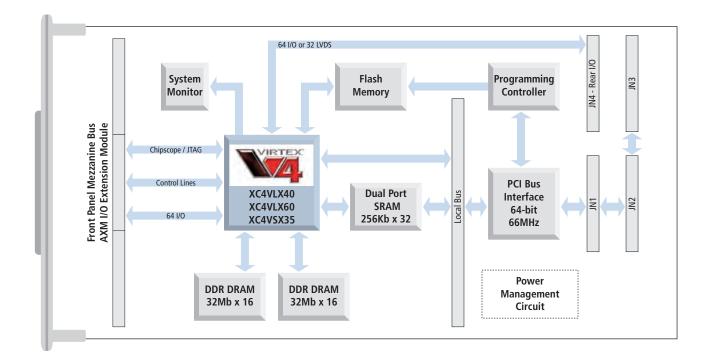

## XMC-SLX User-Configurable Spartan-6 FPGA Modules with Plug-In I/O

## SPARTAN.

XMC module with PCIe interface ◆ Logic-optimized Spartan-6 FPGA ◆ I/O extension mezzanine modules

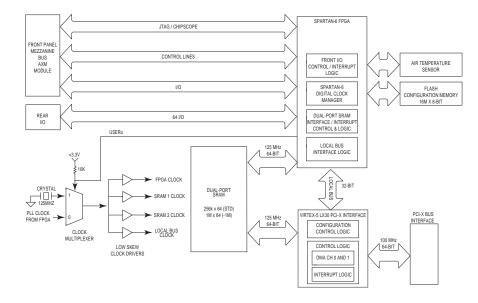

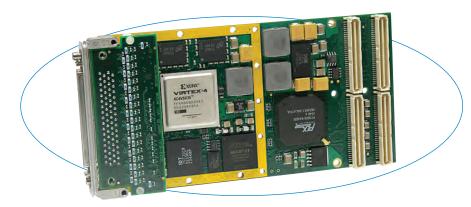

### **Description**

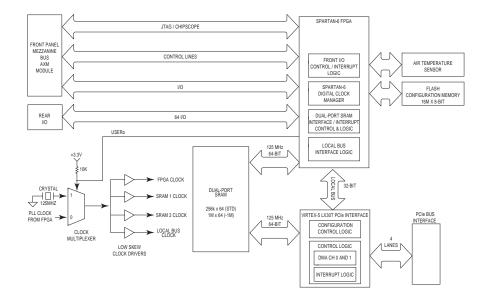

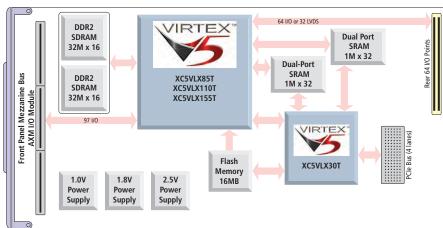

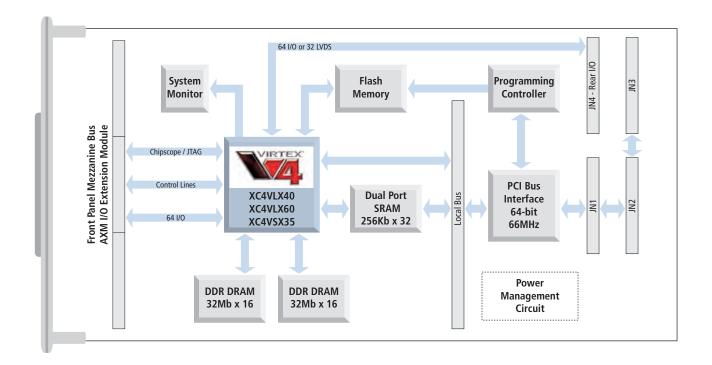

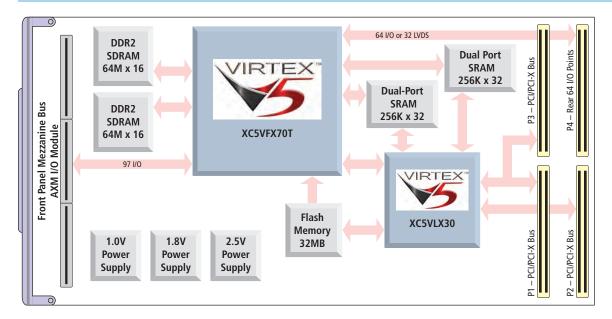

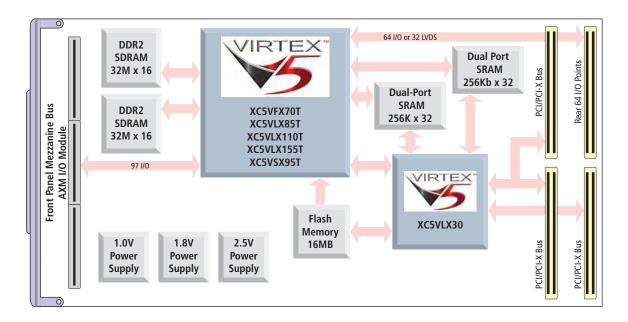

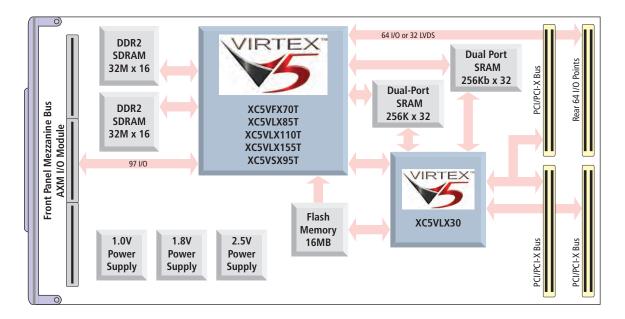

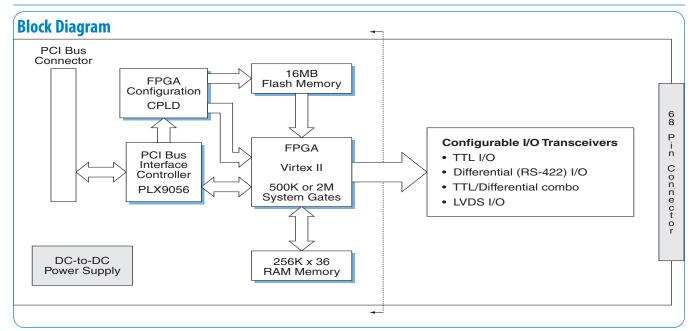

Acromag's cost-effective XMC-SLX modules feature a user-configurable Xilinx® Spartan®-6 FPGA enhanced with high-speed memory and a high-throughput PCle interface. Field I/O interfaces to the FPGA via the rear J4/P4 connector and/or with optional front mezzanine plug-in I/O modules. The result is a powerful and flexible I/O processor module that is capable of executing custom instruction sets and algorithms.

The logic-optimized FPGA is well-suited for a broad range of applications. Typical uses include hardware simulation, communications, in-circuit diagnostics, military servers, signal intelligence, and image processing.

Large, high-speed memory banks enable efficient data handling. The dual-port SRAM facilitates high-speed DMA transfers to the bus or CPU. A high-bandwidth PCIe interface ensures fast data throughput.

64 I/O lines are accessible through the rear (J4) connector. Additional I/O processing is supported on a separate mezzanine card that plugs into the FPGA base board. A variety of these external AXM I/O cards are available to interface your analog and digital I/O signals.

Take advantage of the conduction-cooled design for use in hostile environments. Conduction efficiently dissipates heat if there is inadequate cooling air flow. Optional extended temperature models operate reliably from -40 to 85°C.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board VHDL debugging.

Plug in an AXM analog or digital I/O module for additional I/O signal processing capabilities.

VPX air-cooled and REDI versions are available

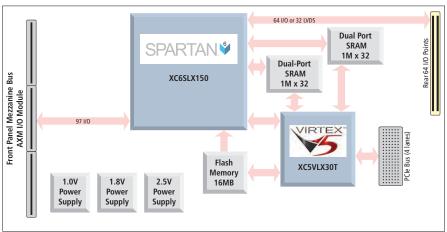

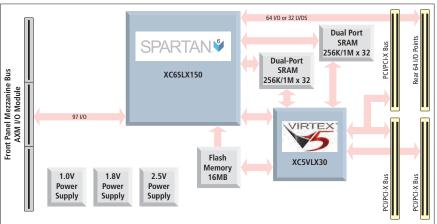

### **Key Features & Benefits**

- Reconfigurable Xilinx Spartan-6 FPGA with 147,433 logic cells

- PCle bus 4-lane Gen 1 interface

- 256k x 64-bit dual-ported SRAM provides direct links from the PCle bus and to the FPGA (optional 1M x 64-bit)

- Supports both front and rear I/O connections

- 64 I/O or 32 LVDS lines direct to FPGA via rear (J4) connector

- Plug-in I/O extension modules are available for the front mezzanine

- FPGA code loads from the PCIe bus or from flash memory

- Other memory options available (call factory)

- Supports dual DMA channel data transfer to the CPU/bus

- Support for Xilinx ChipScope<sup>™</sup> Pro interface

- Designed for conduction-cooled host card or -40 to 85°C operation in air-cooled systems

Tel 248-295-0310 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 Wixom Rd, Wixom, MI 48393 USA

## XMC-SLX User-Configurable Spartan-6 FPGA Modules with Plug-In I/O

### **Performance Specifications**

### **■** FPGA

### FPGA Device

Xilinx Spartan-6 FPGA.

Model XC6SLX150-3FG676 FPGA with 147,433 logic cells and 180 DSP48A1 slices.

### FPGA configuration

Download via PCIe bus or flash memory.

### Example FPGA program

VHDL provided for bus interface, front & rear I/O control, SRAM read/write interface logic, and SDRAM memory interface controller. See EDK kit.

### I/O Processing

Acromag AXM I/O modules:

AXM modules plug into the XMC module's front mezzanine for additional I/O lines. Analog and digital I/O AXM modules are sold separately.

#### Rear I/O

64 I/O (32 LVDS) lines supported with a direct connection between the FPGA and the rear I/O connector (J4).

### ■ Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-SLX module (see www.acromag.com for more information).

### XMC Compliance

Conforms to PCI Express 1.1a electrical and protocol standards. 2.5Gbps data rate per lane per direction.

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

#### Environmental

### Operating temperature

-0 to 70°C or -40 to 85°C (E versions)

### Storage temperature

-55 to 125°C.

#### Relative humidity

5 to 95% non-condensing.

#### Power

3.3V (±5%): 700mA typical, 840mA maximum. 12V (±5%): 640mA typical, 804mA maximum.

#### MTRF