## AP730 and AP731 Multifunction I/O AcroPacks

**Analog Input, Analog Output And Digital I/O Modules**

# **USER'S MANUAL**

## ACROMAG INCORPORATED

30765 South Wixom Road Wixom, MI 48393-2417 U.S.A. Tel: (248) 295-0310

Email: solutions@acromag.com

Copyright 2022, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice.

8501149B

## **Table of Contents**

| 2. GENERAL INFORMATION                                                          |             |

|---------------------------------------------------------------------------------|-------------|

| Preface Trademark, Trade Name and Copyright Information Class A Product Warning |             |

| Trademark, Trade Name and Copyright Information                                 |             |

| Class A Product Warning                                                         |             |

| _                                                                               |             |

| Environmental Protection Statement                                              | 8<br>8<br>8 |

|                                                                                 | 8<br>8<br>9 |

| AcroPack Information – All Models                                               |             |

| Ordering Information                                                            | 9           |

| DAC Key Features                                                                |             |

| ADC Key Features                                                                |             |

| Counter/Timer Key Features                                                      |             |

| Digital Input/Output Key Features                                               |             |

| PCIe Interface Features                                                         |             |

| Signal Interface Products                                                       |             |

| Software Support                                                                |             |

| Windows                                                                         | 12          |

| VxWorks                                                                         | 12          |

| Linux                                                                           | 12          |

| References                                                                      | 13          |

| 3. PREPARATION FOR USE                                                          | 14          |

| Unpacking and Inspection                                                        | 14          |

| Card Cage Considerations                                                        | 14          |

| Board Installation                                                              | 15          |

| Field I/O Connector                                                             | 15          |

| Noise and Grounding Considerations                                              | 18          |

| Logic Interface Connector                                                       | 18          |

| 4. PROGRAMMING INFORMATION                                                      | 20          |

| PCIe Configuration Address Space                                                | 20          |

| Configuration Registers                                                         | 20          |

| BAR0 Memory Map                                                                 | 21          |

| CDMA Memory Map                                                                 | 22          |

| Scatter Gather Memory Map                                                       | 22          |

| AXI-CDMA                                                                        | 22          |

| CDMA Control Register (Read/Write) – (BAR0 + 0x0000)                            | 23          |

| CDMA Status Register (Read/Write) – (BARO + 0x0004)                             | 26          |

| CDMA Current Descriptor Pointer Register (Read/Write) – (BAR0 + 0x0008)         | 29          |

| CDMA Tail Descriptor Pointer Register (Read/Write) – (BAR0 + 0x0010)            | 29          |

|    | CDMA Source Address Register (Read/Write) – (BAR0 + 0x0018)                   | 30 |

|----|-------------------------------------------------------------------------------|----|

|    | CDMA Destination Address Register (Read/Write) – (BAR0 + 0x0020)              | 31 |

|    | CDMA Bytes To Transfer Register (Read/Write) – (BAR0 + 0x0028)                | 31 |

|    | Scatter Gather Transfer Descriptor Definition                                 | 31 |

|    | Transfer Descriptor NXTDESC_PNTR                                              | 32 |

|    | Transfer Descriptor Source Address                                            | 32 |

|    | Transfer Descriptor Destination Address                                       | 33 |

|    | Transfer Descriptor Control Word                                              | 33 |

|    | Transfer Descriptor Status Word                                               | 33 |

|    | Simple CDMA Programming Example                                               | 34 |

|    | (I-BARO Aperture Base Address                                                 |    |

| PC | Cle AXI-Bridge Control                                                        |    |

|    | PHY Status/Control Register (Read) – (BAR + 0x1144)                           |    |

|    | AXI Base Address Translation Configuration Register                           |    |

| In | terrupt Controller                                                            |    |

|    | Interrupt Status Register (Read/Write) – (BARO + 0x2000)                      |    |

|    | Interrupt Pending Register (Read) – (BARO + 0x2004)                           |    |

|    | Interrupt Enable Register (Read/Write) – (BAR0 + 0x2008)                      |    |

|    | Interrupt Acknowledge Register (Write) – (BAR0 + 0x200C)                      |    |

|    | Set Interrupt Enable Register (Write) – (BAR0 + 0x2010)                       | 42 |

|    | Clear Interrupt Enable Register (Write) – (BAR0 + 0x2014)                     | 42 |

|    | Master Enable Register (Read/Write) – (BAR0 + 0x201C)                         | 43 |

| A۶ | (I XADC Analog to Digital Converter (System Monitor) (Read) – (BARO + 0x3000) | 43 |

|    | mware Revision Register (Read) – (BARO + 0x4000)                              |    |

| A> | (I Quad SPI                                                                   |    |

|    | Quad SPI Software Reset Register (Write) – (BAR0 + 0x5040)                    |    |

|    | Quad SPI Control Register (Read/Write) – (BAR0 + 0x5060)                      |    |

|    | Quad SPI Status Register (Read) – (BAR0 + 0x5064)                             |    |

|    | Quad SPI Data Transmit Register (Write) – (BAR0 + 0x5068)                     | 48 |

|    | Quad SPI Data Receive Register (Read) – (BAR0 + 0x506C)                       | 49 |

|    | Quad SPI Slave Select Register (Read/Write) – (BAR0 + 0x5070)                 | 49 |

|    | Quad SPI IP Interrupt Status Register (Read/Write) – (BAR0 + 0x5020)          | 50 |

|    | Serial Flash Write/Read Example                                               | 51 |

| Lo | cation in System Register (Read) – (BARO + 0x6000)                            | 52 |

| Αſ | DC, Digital I/O and Counter Memory Map                                        |    |

|    | Global Interrupt Status Clear Register (Read/Write) – (BARO + 7000H)          | 54 |

|   | Global Interrupt Enable Register (Read/Write) – (BARO + 7004H)                     | 54 |

|---|------------------------------------------------------------------------------------|----|

|   | ADC Control Register (Read/Write) – (BAR0 + 7008H)                                 | 55 |

|   | ADC Range Select Channel Enable Register (Read/Write) – (BAR0 + 700CH)             | 57 |

|   | ADC Conversion Time Register (Read/Write) – (BARO + 7014H)                         | 59 |

|   | ADC FIFO Full Threshold Register (Read/Write) – (BAR0 + 7018H)                     | 60 |

|   | ADC Start Conversion Register (Write) – (BARO + 701C)                              | 60 |

|   | ADC FIFO Channel Data and Tag Register (Read/Write) – (BARO + 7020H)               | 60 |

|   | Modes of Conversion                                                                | 61 |

|   | Programming Considerations                                                         | 62 |

|   | Digital Input/Output Registers (Read/Write) – (BARO + 7040H)                       | 64 |

|   | Digital Direction Control Register (Read/Write) – (BAR0 + 7044H)                   | 64 |

|   | Interrupt Type (COS or H/L) Configuration Register (Read/Write) – (BAR0 + 7048H)   | 65 |

|   | Interrupt Polarity Registers (Read/Write) – (BARO + 704CH)                         | 65 |

|   | Debounce Enable Register (Read/Write) – (BARO + 7050H)                             | 66 |

|   | Debounce Duration Select Register (Read/Write) – (BAR0 + 7054H)                    | 66 |

|   | Counter Trigger, Stop, Load, Readback and Toggle Register (Write) – (BARO + 7070H) | 67 |

|   | Counter Control Register (Read/Write) – (BAR0 + 7074H)                             | 68 |

|   | Counter Interrupt Information Register (Read Only) – (BAR0 + 7078H)                | 82 |

|   | Counter Read Back Register (Read Only) – (BARO + 707CH)                            | 83 |

|   | Counter Constant A Register 1 (Read/Write) – (BARO + 7080H)                        | 83 |

|   | Counter Constant A Register 2 (Read/Write) – (BARO + 7084H)                        | 84 |

|   | Counter Constant B Register 1 (Read/Write) – (BARO + 7088H)                        | 84 |

|   | Counter Constant B Register 2 (Read/Write) – (BAR0 + 708CH)                        | 84 |

|   | ADC Channel X Offset Registers (Read/Write) – (BAR0 + 70A0H to 70DCH)              | 84 |

|   | ADC Channel X Gain Registers (Read/Write) – (BAR0 + 70E0H to 711CH)                | 85 |

| D | AC Registers                                                                       | 86 |

|   | Addressing Sample Memory                                                           | 88 |

|   | Channel X Start Address                                                            | 88 |

|   | Channel X End Address                                                              | 89 |

|   | Channel X FIFO                                                                     | 89 |

|   | Channel X Control Register                                                         | 89 |

|   | Channel X Status Register                                                          | 90 |

|   | Channel X DAC Direct Address                                                       | 91 |

|   | Control Register (Read/Write) – (BARO + 4 0200H)                                   | 93 |

|   | Timer Divider Register (Read/Write) - (RARO + 4 0204H)                             | 93 |

|       | Software Trigger Register (Read/Write) – (BARO + 4 0208H) | 94  |

|-------|-----------------------------------------------------------|-----|

| 5.    | DAC USE OF CALIBRATION DATA                               | 95  |

|       | Uncalibrated Performance                                  |     |

|       | Calibrated Performance                                    | 95  |

| 6.    | ADC USE OF CALIBRATION DATA                               | 99  |

|       | Uncalibrated Performance                                  | 99  |

|       | Calibrated Performance                                    | 99  |

|       | Calibration Programming Example                           | 100 |

|       | Determination of CountCALLO Value                         | 100 |

|       | Determination of CountCALHI Value                         | 101 |

|       | Calculate the Calibration Constants to Store in Flash     | 101 |

| 7.    | FLASH MEMORY MAP                                          | 102 |

|       | DAC Calibration Coefficients (Table 7.1)                  | 102 |

|       | ADC Calibration Coefficients (Table 7.2)                  | 103 |

|       | Flash ASCII String Identifier                             | 104 |

| 8.    | DAC SUGGESTED PROGRAMMING FOR STREAMING MODE              | 105 |

| 9.    | THEORY OF OPERATION                                       | 108 |

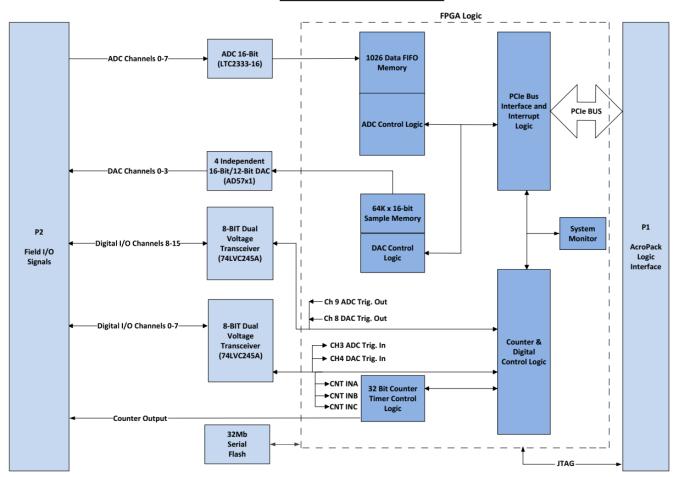

|       | PCIe Interface Logic                                      | 108 |

|       | System Monitor (XADC)                                     | 109 |

|       | Clock Generation                                          | 109 |

|       | 32Mb Serial Flash                                         | 109 |

|       | Counter Timer                                             | 109 |

|       | Digital Input/Output                                      | 109 |

|       | Analog Input                                              | 109 |

|       | Analog Output                                             | 110 |

| 10.   | SERVICE AND REPAIR                                        | 111 |

|       | Service and Repair Assistance                             | 111 |

|       | Preliminary Service Procedure                             | 111 |

|       | Where to Get Help                                         | 111 |

| 11.   | SPECIFICATIONS                                            |     |

|       | Physical                                                  | 112 |

|       | Power                                                     | 112 |

|       | Environmental                                             | 112 |

|       | Reliability Prediction                                    |     |

|       | DAC Analog Output                                         | 113 |

|       | ADC Analog Input                                          | 114 |

|       | Counter/Timers                                            |     |

|       | PCIe Bus Compliance                                       |     |

|       | PCIe Bus Data Rates                                       | 116 |

| Annen | d γih                                                     | 118 |

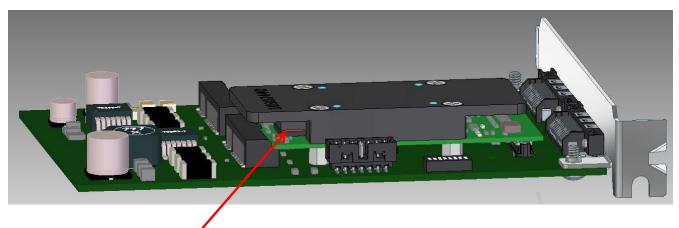

| AP-CC-01 Heatsink Kit Installation | 118 |

|------------------------------------|-----|

| Certificate of Volatility          | 121 |

| REVISION HISTORY                   | 122 |

#### 1. RELATED PUBLICATIONS

The following manuals and part specifications provide the necessary information for an in depth understanding of this product.

ADC Data Sheet LTC2333-16 Buffered 8-Channel, 16-Bit, 800ksps Differential +/-10.24V

DAC Data Sheet AD5761 Multiple Range, 16-Bit, Bipolar/Unipolar (AP730E-LF model only)

DAC Data Sheet AD5721 Multiple Range, 12-Bit, Bipolar/Unipolar (AP731E-LF model only)

## 2. GENERAL INFORMATION

#### **Intended Audience**

This users' manual was written for technically qualified personnel who will be working with I/O devices using the AcroPack module.

#### **Preface**

The information contained in this manual is subject to change without notice, and Acromag, Inc. (Acromag) does not guarantee its accuracy. Acromag makes no warranty of any kind regarding this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Further, Acromag assumes no responsibility for any errors that may appear in this manual and makes no commitment to update, or keep current, the information contained in this manual. No part of this manual may be copied or reproduced in any form, without the prior written consent of Acromag.

#### **Trademark, Trade Name and Copyright Information**

© 2022 by Acromag Incorporated.

All rights reserved. Acromag and Xembedded are registered trademarks of Acromag Incorporated. All other trademarks, registered trademarks, trade names, and service marks are the property of their respective owners.

#### **Class A Product Warning**

This is a Class A product. In a domestic environment this product may cause radio interference, in which case the user may find it necessary to take adequate corrective measures.

#### **Environmental Protection Statement**

Acromag, Inc. Tel: 248-295-0310

This product has been manufactured to satisfy environmental protection requirements where possible. Many components used (structural parts, circuit boards, connectors, etc.) are capable of being recycled. Final

disposition of this product after its service life must be conducted in accordance with applicable country, state, or local laws or regulations.

#### AcroPack Information - All Models

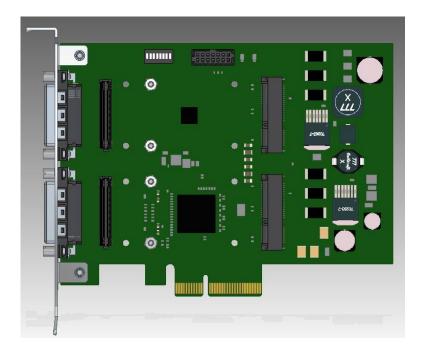

The AcroPack IO modules are based on the PCI Express Mini Card Electromechanical specification and are 70mm in length with an added 100 pin field I/O connector.

The AcroPack is 19.05mm longer than the full length mini PCle card at 50.95mm. It has the same mPCle board width of 30mm and uses the same mPCle standard board hold down standoff and screw keep out areas.

## **Ordering Information**

The AcroPack ordering options are given in the following table.

**Table 2.1 AP73x Modules**

| Model Number | Description                                                 |  |  |  |

|--------------|-------------------------------------------------------------|--|--|--|

| AP730E-LF    | 16 Digital I/O, 8 Differential Analog In (16-Bit), 4 Analog |  |  |  |

|              | Out (16-Bit)                                                |  |  |  |

| AP731E-LF    | 16 Digital I/O, 8 Differential Analog In (16-Bit), 4 Analog |  |  |  |

| Ar / JIL-Li  | Out (12-Bit)                                                |  |  |  |

Operating temperature range: -40°C to 85°C. Applications requiring operating temperatures above 70°C will require purchase of AcroPack Heatsink Accessory AP-CC-01. See Appendix A for installation instructions.

#### **DAC Key Features**

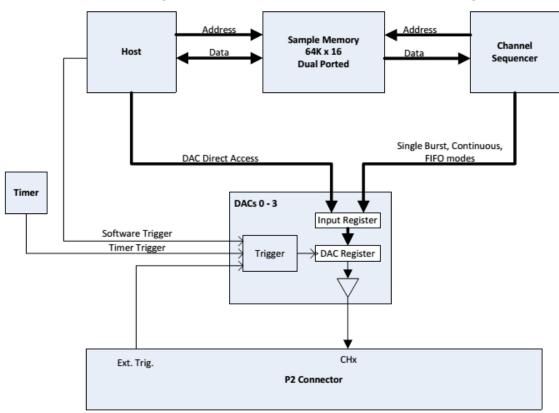

**High Channel Count** – Individual control of four channels of Digital to Analog Converter (DAC) with voltage output is provided.

**Flexible Operating Modes** – Each channel may be independently configured to operate in direct access, single burst, continuous, or streaming (FIFO) mode.

**Flexible Trigger** – Each channel can be independently configured for software trigger, on-board timer trigger, or external trigger mode. The module can accept an external trigger or be the trigger source for synchronizing with other modules.

**Flexible Memory Allocation** – The on-board 64K x 16-bit sample memory is shared among the four channels. The amount of memory allocated to each channel is configurable.

**Continuous Output Mode** - Continuous conversions are implemented by continuously cycling through the waveform memory, from Start Address to End Address, until halted by software. The interval between conversions is controlled by the interval timer. Conversions are initiated by issue of a software or external trigger.

**FIFO Output Mode -** Each of the channel's FIFOs can be filled/loaded with new data without stopping output waveform generation.

**Single Conversion Mode -** Conversions are started with the Start Address and can continue until the channel's End Address is reached.

**AP730, 16-Bit Resolution** - Each channel contains its own 16-bit, Digital to Analog Converter (DAC) with 7.5uS output settling time.

**AP731, 12-Bit Resolution** - Each channel contains its own 12-bit, Digital to Analog Converter (DAC) with 7.5uS output settling time.

**Software selectable output range** - Provides six voltage ranges:

0 to 10 Volts, 0 to 5 Volts, +/-10 Volts, +/-5 Volts, +/-3 Volts, - 2.5V to +7.5 Volts

**Reliable Software Calibration** - Calibration coefficients stored on-board provide the means for accurate software calibration of the module.

#### **ADC Key Features**

Acromag, Inc. Tel: 248-295-0310

**ADC 16-Bit Resolution** - 16-bit capacitor-based successive approximation Analog to Digital Converter (ADC) with integral sample and hold and reference.

**1.264\musec Conversion Time** - A maximum conversion rate of 791,139.24Hz is supported.

**High Density** - Monitors up to 8 differential analog inputs (acquisition mode and channels are selected via programmable control registers).

**1026 Sample FIFO Buffer** – A single 1026 sample deep FIFO is available for buffering data from the 8 differential channels. This allows the external processor to service more tasks within a given time. Data tagging is implemented for easy channel identification. The FIFO buffer can be read through host generated PCle read transactions or through DMA transactions.

**Interrupt Upon FIFO Threshold Reached** – FIFO interrupt generation is also supported. Upon reaching a FIFO programmable threshold condition an interrupt can be generated to minimize CPU interaction.

**Automatic DMA Transfers Upon FIFO Threshold Reached** – In Auto DMA Mode, DMA transfers will automatically be started when the FIFO threshold has been met to minimize CPU interaction.

**FIFO Full, Empty and Threshold Reached Flags** – FIFO Full, Empty and Threshold Reached flag bits are available to implement software polling schemes for FIFO buffer data control.

**Programmable Control of Channels Converted** – Up to 8 differential analog inputs are monitored. Channels 0 to 7 are converted sequentially. Channels may be individually enabled/disabled for conversion.

**User Programmable Conversion Timer** – A programmable conversion timer is available to control the time between conversion of the next channel data.

**Continuous Conversion Mode** – All channels selected for conversion are continually digitized with the interval between conversions controlled by the programmed conversion timer register. Scanning is initiated by a software or external trigger. Scanning is stopped by software control.

**Single Cycle Conversion Mode** – All channels selected for conversion are digitized once with the time between channels controlled by a programmable timer. Single cycle conversion mode is initiated by a software or external trigger.

**External Trigger Input or Output** – The external trigger input is assigned to a field I/O line. The external trigger output is assigned to another field I/O line. This external trigger may be enabled or disabled. As an output, this signal provides a means to synchronize other modules to a single AP73x timer reference.

**Calibration Constants** – Factory calibration constants used to correct gain and offset errors are stored in on-board flash memory. Gain and offset correction constants are stored for each analog to digital channel and each of the supported ranges.

**ADC Ranges Selected via Control Register** - Both bipolar and unipolar ranges are programmable available via control register.

Bipolar ranges of +/-10.24, +/-10, +/-5.12, +/-5.0

Unipolar ranges of +10.24 to 0, +10.0 to 0, +5.12 to 0.

Selected range applies to each channel and can be individually selected on a per channel basis.

#### **Counter/Timer Key Features**

Acromag, Inc. Tel: 248-295-0310

**32-Bit Counter/Timer** – A multifunction 32-bit counter is provided for implementation of: waveform generation, event counting, watchdog timing, pulse-width measurement, or period measurement.

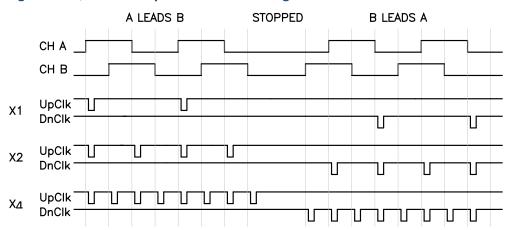

**Quadrature Position Measurement** – Three input signals can be used to determine bi-directional motion. The sequence of logic high pulses for two input signals, A and B, indicate direction and a third signal (index) is used to initialize the counter. X1, X2, and X4 decoding is also implemented. X1 decoding executes one count per duty cycle of the A and B signals, while X2, and X4 execute two and four counts per duty cycle, respectively.

**Pulse Width Modulation** – The counter can be programmed for pulse width modulation. The duration of the logic high and low levels of the output signal can be independently controlled. An external gate signal can also be used to start/stop generation of the output signal.

**Watchdog Timer** – The counter can be configured as a countdown timer for implementation as a watchdog timer. A gate-off signal is available for use to stop the countdown operation. Interrupt generation upon a countdown to zero condition is available.

**Event Counter** – The counter can be configured to count input pulses or events. A gate-off signal is provided to control count-up or count down with each event. Interrupt generation upon programmed count condition is available.

**Frequency Measurement** – The counter can be configured to count how many active edges are received during a period defined by an external count enable signal. An interrupt can be generated upon measurement complete.

**Pulse-Width or Period Measurement** – The counter can be configured to measure pulse-width or waveform period. In addition, an interrupt can be generated upon measurement complete.

**One-Shot and Repetitive One-Shot** – A one-shot pulse waveform may also be generated by the counter. The duration of the pulse and the delay until the pulse goes active is user programmable. A repetitive one-shot can be initiated with repetitive trigger pulses.

**Programmable Interface Polarity** – The polarities of the counter's external trigger, input, and output pins are programmable for active high or low operation. These counter control signals are available through the board's field connector.

**Internal or External Triggering** – A software or hardware trigger is selectable to initiate quadrature position measurement, pulse width modulation, watchdog countdown, event counting, frequency measurement, pulse-width measurement, period measurement, or one-shot operation.

**CMOS Compatible Thresholds** – Input and output signal thresholds are at 3.3-volt levels.

## **Digital Input/Output Key Features**

**16 Digital Input/Output Channels** – Interface with up to 16 input/output channels which can be configured as input or output in groups of eight channels.

**TTL Compatible Thresholds** – Input and output thresholds are at 5V TTL levels. Buffer input channels include hysteresis for increased noise immunity.

**Programmable Change of State/Level Interrupts –** Interrupts are software programmable for any bit Change-Of-State or level on all 16 channels.

**Power Up and System Reset is Failsafe** – For safety, the digital channels are configured for input upon power-up.

#### **PCIe Interface Features**

Acromag, Inc. Tel: 248-295-0310

- PCIe Bus The example design includes a PCI Express Generation 1 interface operating at a bus speed of 2.5 Gbps per lane per direction.

- PCIe Bus Master The PCIe interface logic becomes the bus master to perform DMA transfers.

• **DMA Operation** – The design includes a DMA controller to move data between the FPGA memory and the PCIe bus interface.

• **Compatibility** – PCI Express Base Specification v2.1 compliant PCI Express Endpoint. Provides one interrupt.

## **Signal Interface Products**

This AcroPack Module will mate directly to all Acromag AP carriers. Once connected, the module is accessed via a 50 pin or 68 pin front panel connector.

Accessory cables and termination panels are also available. For optimum performance with the AP73x module, use of the shortest possible length of shielded I/O cable is recommended.

## **Software Support**

The AcroPack series products require support drivers specific to your operating system. Supported operating systems include: Linux®, Windows®, and VxWorks®.

#### **Windows**

Acromag provides software products (sold separately) to facilitate the development of Windows applications interfacing with AcroPack modules, VPX I/O board products, and PCIe I/O Cards. This software (model APSW-API-WIN) consists of low-level drivers and Dynamic Link Libraries (DLLs) that are compatible with a number of programming environments. The DLL functions provide a high-level interface to boards eliminating the need to perform low-level reads/writes of registers, and the writing of interrupt handlers.

#### **VxWorks**

Acromag provides a software product (sold separately) consisting of VxWorks software. This software (Model APSW-API-VXW) is composed of VxWorks (real time operating system) libraries for all AcroPack modules, VPX I/O board products, and PCIe I/O Cards. The software is implemented as a library of "C" functions which link with existing user code to make possible simple control of all Acromag AcroPack modules.

#### Linux

Acromag, Inc. Tel: 248-295-0310

Acromag provides a software product consisting of Linux software. This software (Model APSW-API-LNX) is composed of Linux libraries for all AcroPack modules, VPX I/O board products, and PCIe I/O Cards. The software is implemented as a library of "C" functions which link with existing user code to make possible simple control of all Acromag AcroPack modules.

#### References

The following resources regarding AcroPack modules are available for download on Acromag's website or by contacting your sales representative.

PCI Express MINI Card Electromechanical Specification, REV 1.2 https://www.acromag.com/

#### 3. PREPARATION FOR USE

## IMPORTANT PERSONAL AND PRODUCT SAFETY CONSIDERATIONS

It is very important for the user to consider the possible safety implications of power, wiring, component, sensor, or software failures in designing any type of control or monitoring system. This is especially important where personal injury or the loss of economic property or human life is possible. It is important that the user employ satisfactory overall system design. It is understood and agreed by the Buyer and Acromag that this is the Buyer's responsibility.

WARNING: This board utilizes static sensitive components and should only be handled at a static-safe workstation. This product is an electrostatic sensitive device and is packaged accordingly. Do not open or handle this product except at an electrostatic-free workstation. Additionally, do not ship or store this product near strong electrostatic, electromagnetic, magnetic, or radioactive fields unless the device is contained within its original manufacturer's packaging. Be aware that failure to comply with these guidelines will void the Acromag Limited Warranty.

## **Unpacking and Inspection**

Upon receipt of this product, inspect the shipping carton for evidence of mishandling during transit. If the shipping carton is badly damaged or water stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is absent when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, refer to the Acromag Service Policy to obtain return instructions. It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

This board is physically protected with packing material and electrically protected with an anti-static bag during shipment. It is recommended that the board be visually inspected for evidence of mishandling prior to applying power.

The board utilizes static sensitive components and should only be handled at a static-safe workstation.

## **Card Cage Considerations**

Acromag, Inc. Tel: 248-295-0310

Refer to the specifications section for loading and power requirements. Be sure that the system power supplies are able to accommodate the power requirements of the system boards, plus the installed Acromag board, within the voltage tolerances specified.

In an air-cooled assembly, adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature and

14

to prolong the life of the electronics. If the installation is in an industrial environment and the board is exposed to environmental air, careful consideration should be given to air-filtering.

In a conduction cooled assembly, adequate thermal conduction must be provided to prevent a temperature rise above the maximum operating temperature.

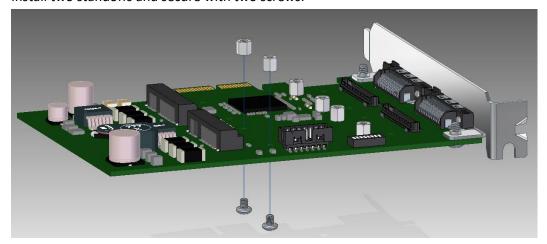

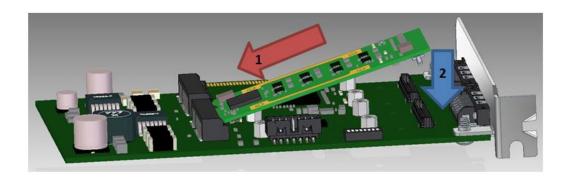

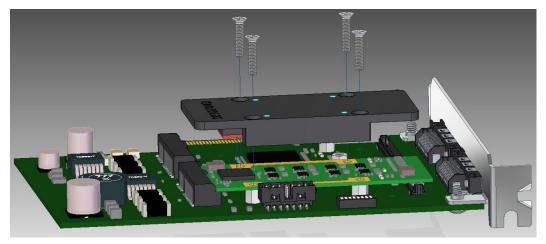

#### **Board Installation**

Power should be removed from the board when installing AP modules, cables, termination panels, and field wiring. The AP73x has no hardware jumpers or switches to configure.

#### Field I/O Connector

The field I/O interface connector P2 provides a mating interface between the AP73x module and the carrier board. Table 3.1 lists pin assignments for each of the AP73x field I/O signals. Every other pin of the 100 pin P2 connector is left unconnected.

IMPORTANT: All unused analog input pins should be tied to analog ground. Floating unused inputs can drift outside the input range causing temporary saturation of the input analog circuits. Recovery from saturation is slow and affects the reading of the desired channels.

Table 3.1 Field I/O Connector Pin Assignments

| Carrier<br>Connector<br>Ribbon <sup>1</sup> | Carrier<br>Connector<br>50 Pin<br>Champ <sup>2</sup> | Carrier<br>Connector<br>68 Pin<br>Champ <sup>3</sup> | Module P2<br>Pin Number | Field I/O Signal |

|---------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------|------------------|

| 1                                           | 1                                                    | 1                                                    | 2                       | Analog In CH0+   |

| 2                                           | 26                                                   | 35                                                   | 1                       | Analog In CH0-   |

| 3                                           | 2                                                    | 2                                                    | 6                       | Analog In CH1+   |

| 4                                           | 27                                                   | 36                                                   | 5                       | Analog In CH1-   |

| 5                                           | 3                                                    | 3                                                    | 10                      | Analog In CH2+   |

| 6                                           | 28                                                   | 37                                                   | 9                       | Analog In CH2-   |

| 7                                           | 4                                                    | 4                                                    | 14                      | Analog In CH3+   |

| 8                                           | 29                                                   | 38                                                   | 13                      | Analog In CH3-   |

| 9                                           | 5                                                    | 5                                                    | 18                      | Analog In CH4+   |

| 10                                          | 30                                                   | 39                                                   | 17                      | Analog In CH4-   |

| 11                                          | 6                                                    | 6                                                    | 22                      | Analog In CH5+   |

| 12                                          | 31                                                   | 40                                                   | 21                      | Analog In CH5-   |

| 13                                          | 7                                                    | 7                                                    | 26                      | Analog In CH6+   |

| 14                                          | 32                                                   | 41                                                   | 25                      | Analog In CH6-   |

| 15                                          | 8                                                    | 8                                                    | 30                      | Analog In CH7+   |

| Carrier<br>Connector<br>Ribbon <sup>1</sup> | Carrier<br>Connector<br>50 Pin<br>Champ <sup>2</sup> | Carrier<br>Connector<br>68 Pin<br>Champ <sup>3</sup> | Module P2<br>Pin Number | Field I/O Signal     |

|---------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------|----------------------|

| 16                                          | 33                                                   | 42                                                   | 29                      | Analog In CH7-       |

| 17                                          | 9                                                    | 9                                                    | 34                      | COMMON               |

| 18                                          | 34                                                   | 43                                                   | 33                      | COMMON               |

| 19                                          | 10                                                   | 10                                                   | 38                      | Analog Out CH0       |

| 20                                          | 35                                                   | 44                                                   | 37                      | COMMON               |

| 21                                          | 11                                                   | 11                                                   | 42                      | Analog Out CH1       |

| 22                                          | 36                                                   | 45                                                   | 41                      | COMMON               |

| 23                                          | 12                                                   | 12                                                   | 46                      | Analog Out CH2       |

| 24                                          | 37                                                   | 46                                                   | 45                      | COMMON               |

| 25                                          | 13                                                   | 13                                                   | 50                      | Analog Out CH3       |

| 26                                          | 38                                                   | 47                                                   | 49                      | COMMON               |

| 27                                          | 14                                                   | 14                                                   | 54                      | COMMON               |

| 28                                          | 39                                                   | 48                                                   | 53                      | COMMON               |

| 29                                          | 15                                                   | 15                                                   | 58                      | Dig CH0/CNT InA      |

| 30                                          | 40                                                   | 49                                                   | 57                      | Dig CH1/CNT InB      |

| 31                                          | 16                                                   | 16                                                   | 62                      | Dig CH2/CNT InC      |

| 32                                          | 41                                                   | 50                                                   | 61                      | Dig CH3/ADC Trig In  |

| 33                                          | 17                                                   | 17                                                   | 66                      | Dig CH4/DAC Trig In  |

| 34                                          | 42                                                   | 51                                                   | 65                      | Dig CH5              |

| 35                                          | 18                                                   | 18                                                   | 70                      | COMMON               |

| 36                                          | 43                                                   | 52                                                   | 69                      | COMMON               |

| 37                                          | 19                                                   | 19                                                   | 74                      | Dig CH6              |

| 38                                          | 44                                                   | 53                                                   | 73                      | Dig CH7              |

| 39                                          | 20                                                   | 20                                                   | 78                      | Dig CH8/DAC Trig Out |

| 40                                          | 45                                                   | 54                                                   | 77                      | Dig CH9/ADC Trig Out |

| 41                                          | 21                                                   | 21                                                   | 82                      | COMMON               |

| 42                                          | 46                                                   | 55                                                   | 81                      | COMMON               |

| 43                                          | 22                                                   | 22                                                   | 86                      | Dig CH10             |

| 44                                          | 47                                                   | 56                                                   | 85                      | Dig CH11             |

| 45                                          | 23                                                   | 23                                                   | 90                      | Dig CH12             |

| 46                                          | 48                                                   | 57                                                   | 89                      | Dig CH13             |

| 47                                          | 24                                                   | 24                                                   | 94                      | Dig CH14             |

| 48                                          | 49                                                   | 58                                                   | 93                      | Dig CH15             |

| 49                                          | 25                                                   | 25                                                   | 98                      | Counter Output       |

| 50                                          | 50                                                   | 59                                                   | 97                      | COMMON               |

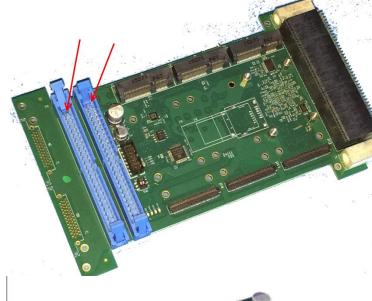

Note 1: VPX4500-CC-LF is an example of a carrier that uses the ribbon cable connector see image of carrier.

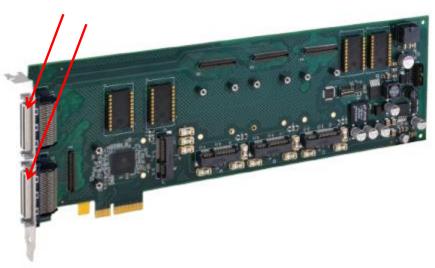

Note 2: APCe7020E-LF is an example of a carrier that uses the 50-pin Champ connector see image of carrier.

Note 3: APCe7040E-LF is an example of a carrier that uses the 68-pin Champ connector see image of carrier.

#### **Noise and Grounding Considerations**

The board is non-isolated, since there is electrical continuity between the logic and field I/O grounds. As such, the field I/O connections are not isolated from the system. Care should be taken in designing installations without isolation to avoid noise pickup and ground loops caused by multiple ground connections.

#### **Logic Interface Connector**

Acromag, Inc. Tel: 248-295-0310

The AP module logic edge connector interfaces to the mating connector on the carrier board. The pin assignments of this connector are standard for all AP modules according to the PCI Express MINI Card Electromechanical Specification, REV 1.2 (with exceptions shown in Table 3.2 and noted below).

Power supplies +5, +12, and -12 Volt have been assigned to pins that are reserved in the mini-PCle specification. The Present signal is grounded on the AP module. In addition, COEX1, COEX2 – wireless transmitter controls, are reassigned to JTAG signals TMS and TCK. Lastly, UIM\_C4, UIM\_C8 – reserved User Identity Module signals are reassigned to JTAG signals TDI and TDO.

18

**Table 3.2 Mini-PCIe Connector**

| Pin #                               | Name                             | Pin # | Name                           |

|-------------------------------------|----------------------------------|-------|--------------------------------|

| 51                                  | +5V <sup>2</sup>                 | 52    | +3.3V <sup>3</sup>             |

| 49                                  | 19 <b>+12V</b> <sup>2</sup>      |       | GND                            |

| 47                                  | -12V <sup>2</sup>                | 48    | +1.5V                          |

| 45                                  | Present <sup>2</sup>             | 46    | N.C. (LED_WPAN#) <sup>1</sup>  |

| 43                                  | GND                              | 44    | N.C. (LED_WLAN#) <sup>1</sup>  |

| 41                                  | +3.3V <sup>3</sup>               | 42    | N.C. (LED_WWAN#) <sup>1</sup>  |

| 39                                  | +3.3V <sup>3</sup>               | 40    | GND                            |

| 37                                  | GND                              | 38    | N.C. (USB_D+) <sup>1</sup>     |

| 35                                  | GND                              | 36    | N.C. (USB_D-) <sup>1</sup>     |

| 33                                  | PETp0                            | 34    | GND                            |

| 31                                  | PETn0                            | 32    | SMB_DATA <sup>4</sup>          |

| 29 GND                              |                                  | 30    | SMB_CLK <sup>4</sup>           |

| 27 GND                              |                                  | 28    | +1.5V                          |

| 25                                  | PERp0                            | 26    | GND                            |

| 23                                  | PERn0                            | 24    | +3.3V <sup>3</sup>             |

| 21                                  | GND                              | 22    | PERST#                         |

| 19                                  | <b>TDI</b> (UIM_C4) <sup>1</sup> | 20    | N.C. (W_DISABLE#) <sup>1</sup> |

| 17 <b>TDO</b> (UIM_C8) <sup>1</sup> |                                  | 18    | GND                            |

| 15                                  | GND                              | 16    | N.C.(UIM_VPP) <sup>1</sup>     |

| 13                                  | RECLK+                           | 14    | N.C.(UIM_RESET) <sup>1</sup>   |

| 11                                  | REFCLK-                          | 12    | N.C.(UIM_CLK) <sup>1</sup>     |

| 9                                   | 9 GND                            |       | N.C.(UIM_DATA) <sup>1</sup>    |

| 7                                   | N.C.(CLKREQ#) <sup>1</sup>       | 8     | N.C.(UIM_PWR) <sup>1</sup>     |

| 5                                   | TCK (COEX2) <sup>1</sup>         | 6     | +1.5V                          |

| 3                                   | TMS (COEX1) <sup>1</sup>         | 4     | GND                            |

| 1 N.C.(WAKE#) <sup>1</sup>          |                                  | 2     | +3.3V <sup>3</sup>             |

- 1. **Note 1:** Signals are not applicable for the AP73x implementation. Pins are either "no connects" on the module or are repurposed for JTAG.

- 2. **Note 2:** +5, +12, and -12 Volt power supplies have been assigned to pins that are reserved in the mini-PCle specification. The Present signal is tied to circuit common on the AP module.

- 3. **Note 3:** All +3.3Vaux power pins are changed to system +3.3V power.

- 4. **Note 4:** The SM bus signals SMB\_CLK and SMB\_DATA will be used to clock a carrier location serial stream from the carrier. These signals are under the control of the AcroPack module.

#### 4. PROGRAMMING INFORMATION

This Section provides the specific information necessary to program and operate the board.

## **PCIe Configuration Address Space**

This AP73x module is PCI Express Base Specification Revision v2.1 compliant.

The PCIe bus is defined to address three distinct address spaces: I/O, memory, and configuration space. This board can be accessed via the PCIe bus memory, and configuration spaces.

The card's configuration registers are initialized by system software at power-up to configure the card. The board is a Plug-and-Play PCIe card. As a Plug-and-Play card the board's base address and system interrupt request are not selected via jumpers but are assigned by system software upon power-up via the configuration registers. A PCIe bus configuration access is used to read/write the PCIe card's configuration registers.

When the computer is first powered-up, the computer's system configuration software scans the PCIe bus to determine what PCIe devices are present. The software also determines the configuration requirements of the PCIe card.

The system software accesses the configuration registers to determine how many blocks of memory space the module requires. It then programs the board's configuration registers with the unique memory base address.

Since this board is not fixed in address space, its device driver must use the mapping information stored in the board's Configuration Space registers to determine where the board is mapped in memory space.

The configuration registers are also used to indicate that the board requires an interrupt request. The system software then programs the configuration registers with the interrupt request assigned to the board.

#### **Configuration Registers**

Acromag, Inc. Tel: 248-295-0310

The PCIe specification requires software driven initialization and configuration via the Configuration Address space. This board provides 512 bytes of configuration registers for this purpose. It contains the configuration registers shown in 4.1 to facilitate Plug-and-Play compatibility.

The Configuration Registers are accessed via the Configuration Address and Data Ports. The most important Configuration Registers are the Base Address Registers and the Interrupt Register which must be read to determine the base address assigned to the board and the interrupt request that goes active on a board interrupt request.

**Table 4.1 Configuration Registers**

| Reg.  | D31                             | D24     | D23      | D16       | D15       | D8         | D7 D0          |

|-------|---------------------------------|---------|----------|-----------|-----------|------------|----------------|

| Num.  |                                 |         |          |           |           |            |                |

| 0     |                                 | Devi    | ce ID    |           |           | Vendo      | or ID          |

|       | 0x7073                          | 3 AP730 | E-LF     |           |           | 16D        | 05             |

|       | 0x7072                          | 2 AP731 | E-LF     |           |           |            |                |

| 1     |                                 | Sta     | itus     |           |           | Comn       | nand           |

| 2     |                                 | (       | Class Co | ode=1180  | 000       |            | Rev ID=00      |

| 3     | BI                              | ST      | He       | eader     | Late      | ency       | Cache          |

| 4:5   | 64-b                            | it Mem  | ory Bas  | e Address | s for Men | nory Acce  | esses to PCIe  |

|       | interrupt, I/O registers, Syste |         |          |           | m Monit   | or registe | ers, and Flash |

|       | me                              |         |          | mory.     |           |            |                |

|       | 1M Space (BAR0)                 |         |          |           |           |            |                |

| 6:10  | Not Used                        |         |          |           |           |            |                |

| 11    | Subsystem ID                    |         |          | )         | Sub       | system \   | Vendor ID      |

|       | 0x7073 AP730E-LF                |         |          |           | 16D       | <b>)</b> 5 |                |

|       | 0x7072 AP731E-LF                |         |          |           |           |            |                |

| 12    | Not Used                        |         |          |           |           |            |                |

| 13,14 | Reserved                        |         |          |           |           |            |                |

| 15    | Max                             | _Lat    | Mir      | n_Gnt     | Inter     | r. Pin     | Inter. Line    |

This board is allocated a 1M byte block of memory (BARO), to access the PCIe interrupt, DAC registers, ADC registers, Counter Timer registers, Digital I/O registers, XADC registers, Flash memory.

## **BAR0 Memory Map**

Acromag, Inc. Tel: 248-295-0310

The BARO memory address space is used to access the devices listed in the table below. Note that the base address for the board (BARO) in memory space must be added to the addresses shown to properly access these registers.

**Table 4.2 BAR0 Registers**

| BAR0 Base Address                   | Size | Description                                            |

|-------------------------------------|------|--------------------------------------------------------|

| 0x0000_0000->0x0000_0FFF            | 4K   | CDMA (see Xilinx Document PG034)                       |

| 0x0000_1000→0x0000_1FFF             | 4K   | PCIe AXI Bridge Control (see<br>Xilinx Document PG054) |

| 0x0000_2000→0x0000_2FFF             | 4K   | Interrupt Controller                                   |

| 0x0000_3000->0x0000_3FFF            | 4K   | XADC System Monitor (see<br>Xilinx Document DS790)     |

| 0x0000_4000→0x0000_4FFF             | 4K   | <u>Firmware Revision</u>                               |

| 0x0000_5000→0x0000_5FFF             | 4K   | Flash AXI QSPI                                         |

| 0x0000_6000→0x0000_6FFF             | 4K   | <u>Location in System</u>                              |

| 0x0000_7000→0x0000_7FFF             | 4K   | M07 AXI Custom (ADC,<br>Counter, Digital I/O)          |

| 0x0000_8000→0x0000_FFFF             | 32K  | Reserved                                               |

| 0x0001_0000 \rightarrow 0x0001_7FFF | 32K  | Block RAM                                              |

| BAR0 Base Address                   | Size | Description              |

|-------------------------------------|------|--------------------------|

| 0x0001_8000→0x0003_FFFF             | 164K | Reserved                 |

| 0x0004_0000 \rightarrow 0x0004_0213 | 1K   | DAC Registers            |

| 0x0004_0214→0x0005_FFFF             | 127K | Reserved                 |

| 0x0006 0000→0x0007 FFFF             | 128K | Sample Memory            |

| 0x0006_0000-70x0007_FFFF            |      | Part of DAC Memory space |

| 0x0008_0000 → 0x000F_FFFF           | 524K | AXI to PCIe BARO         |

#### **CDMA Memory Map**

The Central Direct Memory Access (CDMA) controller can access the AXI to PCI bridge (BARO), the ADC FIFO memory, and the DAC Sample Memory.

**Table 4.3 CDMA Memory Map**

| BARO Base Address                      | Size | Description                  |

|----------------------------------------|------|------------------------------|

| 0x0000 1000→0x0000 1FFF                | 4K   | PCIe AXI Bridge Control (see |

| 0x0000_1000->0x0000_1FFF               | 4K   | Xilinx Document PG054)       |

| 0x0000 7000→0x0000 7FFF                | 4K   | M07 AXI Custom (ADC,         |

| 0x0000_7000-70x0000_7FFF               |      | Counter, Digital I/O)        |

| 0x0001_0000 → 0x0001_7FFF              | 32K  | Block RAM                    |

| 0x0004_000 <del>&gt;</del> 0x0004_0213 | 1K   | DAC Registers                |

| 0x0004_0214→0x0005_FFFF                | 127K | Reserved                     |

| 0x0006_0000 → 0x0007_FFFF              | 128K | Sample Memory                |

## **Scatter Gather Memory Map**

Acromag, Inc. Tel: 248-295-0310

The scatter-gather engine can access the block RAM Memory only. The scatter-gather descriptor list must be located in this memory. The block RAM can hold 512 descriptors (64 bytes/Descriptor).

**Table 4.4 Scatter Gather Memory Map**

| BAR0 Base Address       | Size | Description |

|-------------------------|------|-------------|

| 0x0001_0000→0x0001_7FFF | 32K  | Block RAM   |

#### **AXI-CDMA**

The AXI Central Direct Memory Access (CDMA) core is a soft Xilinx Intellectual Property core. The CDMA provides direct memory access between system memory over the PCIe bus and the memory resident on the XCM730 module.

The basic mode of operation for the CDMA is Simple DMA. In this mode, the CDMA executes one programmed DMA command and then stops. This requires that the CDMA registers need to be set up by system software over the PCIe bus for each DMA operation required.

Scatter Gather is a mechanism that allows for automated DMA transfer scheduling via a pre-programmed instruction list of transfer descriptors. This instruction list is programmed by the user software application into a memory-resident data structure that must be accessible by the AXI CDMA Scatter Gather interface. This list of instructions is organized into what is

referred to as a transfer descriptor chain. Each descriptor has an address pointer to the next descriptor to be processed. The last descriptor in the chain generally points back to the first descriptor in the chain but it is not required. The AXI CDMA Tail Descriptor Pointer register needs to be programmed with the address of the first word of the last descriptor of the chain. When the AXI CDMA executes the last descriptor and finds that the Tail Descriptor pointer register contents matches the address of the completed descriptor, the Scatter Gather Engine stops descriptor fetching and waits. See the Xilinx AXI Central Direct Memory Access product guide PG034 for additional details for Scatter Gather operations.

Table 4.5 AXI-CDMA

| BAR0 Base Addr+ | Bit(s) | Description                  |

|-----------------|--------|------------------------------|

| 0x0000_0000     | 31:0   | CDMA Control Register        |

| 0x0000_0004     | 31:0   | CDMA Status Register         |

| 0x0000 0008     | 31:0   | Current Descriptor Pointer   |

| 0x0000_0008     | 31.0   | Register                     |

| 0x0000_000C     | 31:0   | Reserved                     |

| 0x0000 0010     | 31:0   | Tail Descriptor Pointer      |

| 0x0000_0010     |        | Register                     |

| 0x0000_0014     | 31:0   | Reserved                     |

| 0x0000_0018     | 31:0   | Source Address Register      |

| 0x0000_001C     | 31:0   | Reserved                     |

| 0x0000_0020     | 31:0   | Destination Address Register |

| 0x0000_0024     | 31:0   | Reserved                     |

| 0x0000_0028     | 31:0   | Bytes to Transfer Register   |

Note that any registers/bits not mentioned will remain at the default value: logic low.

## CDMA Control Register (Read/Write) – (BAR0 + 0x0000)

This register provides software application control of the AXI CDMA.

Table 4.6 CDMA Control Register (Read/Write) – (BAR0 + 0x0000)

| Bit(s) | Fun                                                                                       | ction                                                |  |  |

|--------|-------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| 0      | This bit is reserved for future definition and will always                                |                                                      |  |  |

| U      | retu                                                                                      | ırn zero.                                            |  |  |

| 1      | The                                                                                       | The bit will always return one.                      |  |  |

|        | Soft reset control for the AXI CDMA core.                                                 |                                                      |  |  |

|        | Setting this bit to a '1' causes the AXI CDMA to be reset.                                |                                                      |  |  |

|        | Rese                                                                                      | et is accomplished gracefully. Committed AXI4        |  |  |

| 2      | tran                                                                                      | sfers are then completed. Other queued transfers are |  |  |

| 2      | flushed. After completion of a soft reset, all registers and bits are in the Reset State. |                                                      |  |  |

|        |                                                                                           |                                                      |  |  |

|        | 0                                                                                         | Reset Not in Progress                                |  |  |

|        | 1                                                                                         | Reset in Progress                                    |  |  |

| Bit(s) | Function                                                                        |  |  |

|--------|---------------------------------------------------------------------------------|--|--|

| (-)    | This bit controls the transfer mode of the CDMA. Setting                        |  |  |

|        | this bit to a '1' causes the AXI CDMA to operate in a                           |  |  |

|        | Scatter Gather mode.                                                            |  |  |

|        |                                                                                 |  |  |

|        | Note: This bit must only be changed when the CDMA                               |  |  |

|        | engine is IDLE (CDMA Status bit-1 = '1'). Changing the                          |  |  |

|        | state of this bit at any other time has undefined results.                      |  |  |

| 3      | Note: This bit must be set to a 0 then back to 1 by the                         |  |  |

|        | software application to force the CDMA Scatter Gather                           |  |  |

|        | engine to use a new value written to the CDMA Current                           |  |  |

|        | Descriptor Pointer register.                                                    |  |  |

|        | Note: This bit must be set prior to setting Bit-13 of this                      |  |  |

|        | CDMA Control register.                                                          |  |  |

|        | 0 Simple DMA Mode                                                               |  |  |

|        | 1 Scatter Gather Mode                                                           |  |  |

|        | This bit enables the keyhole read (FIXED address AXI                            |  |  |

|        | transaction).                                                                   |  |  |

|        |                                                                                 |  |  |

|        | Note: This value should not be changed when a transfer is                       |  |  |

|        | in progress. This value should remain constant until all the                    |  |  |

| 4      | descriptors are processed (for SG = 1). CDMA shows                              |  |  |

| 7      | unexpected behavior if the value is changed in the middle                       |  |  |

|        | of a transfer.                                                                  |  |  |

|        | Note: It is the responsibility of the slave device to enforce                   |  |  |

|        | the functionality.                                                              |  |  |

|        | 0 Key Hole Read Disabled                                                        |  |  |

|        | 1 Key Hole Read Enabled                                                         |  |  |

|        | Key Hole Write.                                                                 |  |  |

|        | Writing 1 to this enables the keyhole write (FIXED address                      |  |  |

|        | AXI transaction). This value should not be changed when a                       |  |  |

| _      | transfer is in progress. This value should remain constant                      |  |  |

| 5      | until all the descriptors are processed (for SG = 1). CDMA                      |  |  |

|        | shows unexpected behavior if this value is changed in the middle of a transfer. |  |  |

|        | 0 Key Hole Write Disabled                                                       |  |  |

|        | 1 Key Hole Write Enabled                                                        |  |  |

|        | Cyclic BD Enable.                                                               |  |  |

| 6      | When set to 1, you can use the CDMA in Cyclic Buffer                            |  |  |

|        | Descriptor (BD) mode without any user intervention. In                          |  |  |

|        | this mode, the Scatter Gather module ignores the                                |  |  |

|        | Completed bit of the BD. With this feature, you can use                         |  |  |

|        | the same BDs in cyclic manner without worrying about any                        |  |  |

|        | errors.                                                                         |  |  |

|        | This bit should be set before updating the TAILDESC                             |  |  |

|        | register. Changing this bit while the transfer is in progress                   |  |  |

|        | will generate undefined results.                                                |  |  |

| D:+/a\ | F                                                                                                | ation.                                                     |  |

|--------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| Bit(s) | Function  Ouglie RD Disabled                                                                     |                                                            |  |

|        | 0 Cyclic BD Disabled                                                                             |                                                            |  |

| 44 7   | 1                                                                                                | Cyclic BD Enabled                                          |  |

| 11-7   | Reserved                                                                                         |                                                            |  |

|        |                                                                                                  | errupt on Complete Interrupt Enable.                       |  |

|        | When set to '1', it allows an interrupt after complete                                           |                                                            |  |

| 12     |                                                                                                  | A transfers.                                               |  |

|        | 0                                                                                                | Interrupt on Complete Disabled                             |  |

|        | 1                                                                                                | Interrupt on Complete Enabled                              |  |

|        |                                                                                                  | errupt on Delay Timer Interrupt Enable.                    |  |

|        |                                                                                                  | en set to '1', it allows a delayed interrupt out. This is  |  |

| 13     | onl                                                                                              | y used with Scatter Gather assisted transfers.             |  |

|        | 0                                                                                                | Delayed Interrupt Disabled                                 |  |

|        | 1                                                                                                | Delayed Interrupt Enabled                                  |  |

|        | Inte                                                                                             | errupt on Error Interrupt Enable.                          |  |

|        | Wh                                                                                               | en set to '1', it allows an error to generate an interrupt |  |

| 14     | out                                                                                              |                                                            |  |

|        | 0                                                                                                | Error Interrupt Disabled                                   |  |

|        | 1                                                                                                | Error Interrupt Enabled                                    |  |

| 15     | Res                                                                                              | erved                                                      |  |

|        | Inte                                                                                             | errupt Threshold value.                                    |  |

|        | This                                                                                             | s field is used to set the Scatter Gather interrupt        |  |

|        |                                                                                                  | lescing threshold. When Interrupt On Complete              |  |

|        | inte                                                                                             | errupt events occur, an internal counter counts down       |  |

|        | from the Interrupt Threshold setting. When the count                                             |                                                            |  |

|        |                                                                                                  | reaches zero, an interrupt out is generated by the CDMA    |  |

| 23-16  |                                                                                                  | rine.                                                      |  |

|        |                                                                                                  | , -                                                        |  |

|        | Not                                                                                              | e: The minimum setting for the threshold is 0x01. A        |  |

|        | write of 0x00 to this register has no effect. If the CDMA is                                     |                                                            |  |

|        |                                                                                                  | It with Scatter Gather disabled (Simple Mode Only), the    |  |

|        |                                                                                                  | ault value of the port is zeros.                           |  |

|        |                                                                                                  | errupt Delay Time Out.                                     |  |

|        |                                                                                                  | s value is used for setting the interrupt delay time out   |  |

|        | value. The interrupt time out is a mechanism for causing                                         |                                                            |  |

|        | the CDMA engine to generate an interrupt after the delay                                         |                                                            |  |

| 31-24  | time period has expired. This is used for cases when the                                         |                                                            |  |

|        | interrupt threshold is not met after a period of time, and                                       |                                                            |  |

|        | the CPU desires an interrupt to be generated. Timer                                              |                                                            |  |

|        |                                                                                                  | ins counting when the CDMA is IDLE (CDMA Status bit-       |  |

|        | _                                                                                                | '1'). This generally occurs when the CDMA has              |  |

|        |                                                                                                  | npleted all scheduled work defined by the transfer         |  |

|        |                                                                                                  | ·                                                          |  |

|        | descriptor chain (reached the tail pointer) and has not satisfied the Interrupt Threshold count. |                                                            |  |

|        | Sati                                                                                             | sned the interrupt threshold count.                        |  |

|        | Not                                                                                              | ca. Catting this value to zero disables the delay times.   |  |

|        |                                                                                                  | te: Setting this value to zero disables the delay timer    |  |

|        | inte                                                                                             | errupt.                                                    |  |

## CDMA Status Register (Read/Write) – (BAR0 + 0x0004)

This register provides status of the AXI CDMA.

Table 4.7 CDMA Status Register (Read/Write) – (BAR0 + 0x0004)

| Bit(s) | Function                                                                                                              |  |

|--------|-----------------------------------------------------------------------------------------------------------------------|--|