# Series PMC-SLX150

**Spartan 6 Based FPGA**

**PMC Module**

# Getting Started with the PMC-SLX Engineering Design Kit

# ACROMAG INCORPORATED

30765 South Wixom Road P.O. BOX 437 Wixom, MI 48393-7037 U.S.A. Tel: (248) 624-1541 Fax: (248) 624-9234

Copyright 2013, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice.

8500-924-B13C012

# Table of Contents

| GETTING STARTED                                                  | 2  |

|------------------------------------------------------------------|----|

| Installing the Board and Device Drivers                          | 2  |

| Starting a New Xilinx Project                                    | 3  |

| Modifying the Provided VHDL Code                                 |    |

| Example Change                                                   | 8  |

| Simulating the Example Design Using ISIM                         | 12 |

| Generating a Programming "MCS" File                              | 18 |

| Differences in VHDL between the XMC-SLX150 and the XMC-SLX150-1M | 25 |

| Xilinx ISE 13.2 Compiler Warnings                                | 26 |

All trademarks are the property of their respective owners.

You must consider the possible negative effects of power, wiring, component, sensor, or software failure in the design of any type of control or monitoring system. This is very important where property loss or human life is involved. It is important that you perform satisfactory overall system design and it is agreed between you and Acromag, that this is your responsibility.

# **Getting Started**

|                                            | The purpose of this document is to provide basic instructions on using the "PMC-SLX Engineering Design Kit" with the PMC-SLX Boards. It will focus on programming the FPGA of the PMC-SLX150 using VHDL, but can be easily modified to use with any model of the SLX line. This document also shows how to use the supplied DLL files with a MFC application. It is assumed that the user has a working knowledge of Xilinx, VHDL and Visual C++. Note that this document assumes Windows is used as the operating systems. Linux users can follow the same general procedure but be aware that differences exist that are not noted in this document.                                                                                                               |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | There are small differences in the VHDL between the PMC-SLX150(E) and the PMC-SLX150(E)-1M models due to differences in the SRAM size. Refer to the appendix at the end of this manual for further information on the VHDL differences.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Installing the Board<br>and Device Drivers | For first time users, turn off your computer, and unplug the power cord.<br>Before touching either board, make sure to discharge all static electricity.<br>Then attach the SLX150 to your carrier. Insert the carrier into an empty slot<br>in your computer. When restarting your computer, you will be prompted to<br>insert a CD with the drivers on it. At this point, insert the PCISW-API-WIN<br>CD (software product sold separately from this EDK) into your CD-ROM<br>drive. When the plug and play installation has completed, follow the steps<br>to install the additional PCISW-API-WIN software on your computer. When<br>finished, insert the CD titled <b>PMC-SLX Engineering Design Kit</b> and copy the<br><b>SLX150</b> folder to your computer. |

|                                            | Before you start, familiarize yourself with the <b>PMC-SLX User's Manual</b> included on the EDK CD and the <b>PCISLX Driver Function Reference</b> included on the PCI Win32 Driver Software CD. The user's manual gives the memory addresses of all the registers, and their purposes. The function reference gives information on how to use the DLL file in C/C++, Visual Basic, and LabView (we will be focusing only on using the C/C++ demo program).                                                                                                                                                                                                                                                                                                         |

|                                            | A readme.txt file is included on the EDK CD. This file contains detailed information on the contents of the CD including a description of the contents of the VHDL files. Read this file prior to reading this manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                            | This manual assumes that Xilinx ISE Version 13.2 in used. Note that earlier versions are not supported and later versions may have alternate procedures. Also note that VHDL line numbers in this manual may not match the line numbers of the files provided in the EDK due to revisions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## **Starting a New Xilinx Project**

- Make a new directory on your computer and call it XC6SLX150.

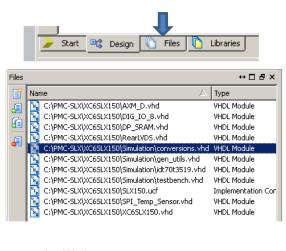

- From the XC6SLX150 folder, copy the all the vhdl files in into the new XC6SLX150 folder. Then from the XC6SLX150 folder copy the SLX150.ucf file to the XC6SLX150 folder. Note that all of the files are shown in the adjacent figure.

- Start Xilinx's Project

Navigator from your start

menu. Xilinx ISE Design

Suite 13.2 → ISE Design

Tools → Project Navigator

- Open a new project by selecting File → New Project

In the Project Name field, type SLX150. In the Location field type the path name where to find the XC6SLX150 folder. Make sure the Top-Level Module Type field is HDL, and click Next.

Enter the following information if using the SLX150. Then click Next and then Finish.

Family: Spartan6

Device: XC6SLX150

Package: FGG676

Speed: -3

| <mark>&gt; New Project Wiza</mark>        | rd 🛛 🛛 🔀                                                      |

|-------------------------------------------|---------------------------------------------------------------|

| Create New Project<br>Specify project loc | ation and type.                                               |

| -Enter a name, locatio                    | ons, and comment for the project                              |

| N <u>a</u> me:                            | SLX150                                                        |

| Location:                                 | C:\Designs\PMC_SLX150\Spartan_FPGA\PMC-SLX150\X6SLX150\SLX150 |

| Working Directory:                        | C:\Designs\PMC_SLX150\Spartan_FPGA\PMC-SLX150\X6SLX150\SLX150 |

| Description:                              |                                                               |

| -Select the type of to                    | p-level source for the project                                |

| <u>T</u> op-level source typ              |                                                               |

| HDL                                       |                                                               |

| More Info                                 | Next > Cancel                                                 |

| elect the device and design flow for th |                     |   |

|-----------------------------------------|---------------------|---|

| Property Name                           | Value               |   |

| Product Category                        | All                 | ~ |

| Family                                  | Spartan6            | ~ |

| Device                                  | XC65LX150           | ~ |

| Package                                 | FGG676              | ~ |

| Speed                                   | -3                  | ~ |

| Top-Level Source Type                   | HDL                 | ~ |

| Synthesis Tool                          | XST (VHDL/Verilog)  | ~ |

| Simulator                               | ISim (VHDL/Verilog) | ~ |

| Preferred Language                      | VHDL                | ~ |

| Property Specification in Project File  | Store all values    | ~ |

| Manual Compile Order                    |                     |   |

| VHDL Source Analysis Standard           | VHDL-93             | ~ |

| Enable Message Filtering                |                     |   |

| Enable Message Filtening                |                     |   |

- We will next add the files we copied from the CD. Follow these steps:

- a. Select **Project->Add Source**.

- b. Select the .ucf and all the .vhd files

- c. Click the **Open** button.

- d. The association for all files should be *All* for the .vhd files and *Implement* for the .ucf files. There are a total of 6 .vhd files and one .ucf file.

- e. Click the OK button.

- In the Heirarchy Window, click on XC6SLX150\_arch (XC6SLX150.vhd) to highlight it.

The following allows you to see the status of the source files being added to the project. It also allows you to specify the Design View association, and for VHDL sources the library, for sources which are successfully added to the project.

|   | File Name           | Association    |   | Library |   |

|---|---------------------|----------------|---|---------|---|

| 1 | 🔇 XC6SLX150.vhd     | All            | ~ | work    | Y |

| 2 | 📀 AXM_D.vhd         | All            | ~ | work    | Y |

| 3 | 📀 DIG_IO_8.vhd      | All            | ~ | work    | Y |

| 4 | 📀 DP_SRAM.vhd       | All            | ~ | work    | v |

| 5 | 📀 RearLVDS.vhd      | All            | ~ | work    | v |

| 6 | 📀 SLX150.ucf        | Implementation | ~ | work    | v |

| 7 | SPI_Temp_Sensor.vhd | All            | × | work    | ~ |

|   |                     |                |   |         |   |

|   |                     |                |   |         |   |

| Desi | gn ↔□ð×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ľ    | View: 💿 🄯 Implementation 🔿 🧱 Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6    | Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ۵.   | SLX150 xc6slx150-3fgg676                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | XC65LX150 - XC65LX150_arch (XC65LX150.vhd)         No         DPSRAM - DP_SRAM - DP_SRAM_ARCH (DP_SR         AXM_Module - AXM_D - AXM_D_arch (AXM_D.vhd)         No         No |

Click on the Startup

Options tab and verify the

following options are

selected:

Note that if not all properties are shown change the Property display level from Standard to Advanced.

12. Click on the **Configuration Options** tab. Verify that all options are set to default as shown in the screen shot to the right.

13. Click **OK**.

| FPGA Start-up Clock:       | CCLK        |

|----------------------------|-------------|

| Enable Internal Done Pipe: | Not Checked |

| Done                       | 6           |

| Enable Outputs:            | 5           |

| Release Write Enable:      | 5           |

| Wait for DCM and PLL Lock: | NoWait      |

| Drive Done Pin High:       | Checked     |

**Second States - Startup Options** × <u>C</u>ategory Value Switch Name Property Name General Options -g StartUpClk: FPGA Start-Up Clock CCLK ¥ Configuration Options -g DonePipe: Startup Options Enable Internal Done Pipe Readback Options -g DONE\_cycle: Done (Output Events) 6 ¥ Encryption Options -g GTS\_cycle: Enable Outputs (Output Events) Default (5) ¥ Suspend/Wake Options -g GWE\_cycle: Release Write Enable (Output Events) 5 ~ Wait for DCM and PLL Lock (Output Events) Default (NoWait) 🗸 -g LCK\_cycle: -g DriveDone: Drive Done Pin High **~** Property display level: Advanced 🔽 🗹 Display switch names <u>D</u>efault OK Cancel Apply Help

| lategory                                                         | Switch Name               | Property Name                                        | Value              |

|------------------------------------------------------------------|---------------------------|------------------------------------------------------|--------------------|

| General Options<br>Configuration Options                         | -g ConfigRate:            | Configuration Rate                                   | 2                  |

| Startup Options                                                  | -g ProgPin:               | Configuration Pin Program                            | Pull Up            |

| Readback Options     Encryption Options     Suspend/Wake Options | -g DonePin:               | Configuration Pin Done                               | Pull Up            |

|                                                                  | -g TckPin:                | JTAG Pin TCK                                         | Pull Up<br>Pull Up |

|                                                                  | -g TdiPin:                | JTAG Pin TDI                                         | Pull Up            |

|                                                                  | -g TdoPin:                | JTAG Pin TDO                                         | Pull Up            |

|                                                                  | -g TmsPin:                | JTAG Pin TMS                                         | Pull Up            |

|                                                                  | -g UnusedPin:             | Unused IOB Pins                                      | Pull Down          |

|                                                                  | -g UserID:                | UserID Code (8 Digit Hexadecimal)                    | 0×FFFFFFFF         |

|                                                                  | -g ExtMasterCclk_en:      | Enable External Master Clock                         |                    |

|                                                                  | -g ExtMasterCclk_divide:  | Setup External Master Clock Division                 | 1                  |

|                                                                  | -g SPI_buswidth:          | Set SPI Configuration Bus Width                      | 1                  |

|                                                                  | -g TIMER_CFG:             | Watchdog Timer Value                                 | 0×FFFF             |

|                                                                  | -                         | Place MultiBoot Settings into Bitstream              |                    |

|                                                                  | -g next_config_addr:      | MultiBoot: Starting Address for Next Configuration   | 0x00000000         |

|                                                                  | -g next_config_new_mode:  | MultiBoot: Use New Mode for Next Configuration       |                    |

|                                                                  | -g next_config_boot_mode: | MultiBoot: Next Configuration Mode                   | 001                |

|                                                                  | -g golden_config_addr:    | MultiBoot: Starting Address for Golden Configuration | 0×00000000         |

|                                                                  | -g failsafe_user:         | MultiBoot: User-Defined Register for Failsafe Scheme | 0×0000             |

|                                                                  | F                         | Property display level: Advanced 💽 🗹 Display swi     | itch names Default |

|                                                                  |                           | OK Cancel                                            | Apply Help         |

201

### Modifying the Provided VHDL Code

To revise or add to the provided VHDL code, begin by double clicking on the **XC6SLX150-XC6SLX150\_arch (XC6SLX150.vhd)** file located in the **Hierarchy** window. This will open the VHDL file for editing.

Additional components and signals may be added between the current definitions at line 288.

-- Temperature Sensor Signals -----285 286 signal TEMP\_Sen\_Strobe : STD\_LOGIC; signal TEMP DATA: STD LOGIC VECTOR(12 downto 0); 287 288 289 component DP SRAM 290 291 port( 292 293 --Global signal -----CLK: in STD LOGIC; 294 RESET: in STD LOGIC; 295 296

After the **begin** keyword (line 491) additional instantiations for components may be added

| 485 | <pre>TEMP_SDO : in STD_LOGIC SPI Data Input.</pre> |

|-----|----------------------------------------------------|

| 486 |                                                    |

| 487 | );                                                 |

| 488 | end component;                                     |

| 489 |                                                    |

| 490 |                                                    |

| 491 | begin                                              |

| 492 |                                                    |

| 493 | <pre>SRR_INTn &lt;= SR_INTn or SR3_INTn;</pre>     |

| 494 | SRR_COLn <= SR_COLn or SR3_COLn;                   |

| 495 |                                                    |

| 496 | SR3_CE1 <= '1';                                    |

| 497 | <pre>SR1_CE1 &lt;= '1';</pre>                      |

| 408 |                                                    |

For simplicity we suggest starting by adding to or revising the provided VHDL code that is associated with the front I/O. To use the front I/O, begin by double clicking on the **AXM\_Module-AXM\_D\_arch (AXM\_D.vhd)** file located in the **Hierarchy** window. This will open the VHDL file for editing. To use the rear I/O, begin by double clicking on the **Rear\_IO-RearLVDS\_arch (RearLVDS.vhd)** file located in the **Hierarchy** window. This will likewise open the VHDL file associated with the rear I/O for editing

#### **Example Change**

Below is a simple example of some VHDL that could be used to control five of the SLX150's Front I/O differential channels (via the AXM-D02 or AXM-D04). It is included to show how the code supplied with the Engineering Design Kit can be modified for personal use.

```

200 signal Int_Polarity_Adr : STD_LOGIC; --0x801C

201

202 --Here we add the decode signal for the

203 --new counter address that we are going to send

204 --to the AXM

205 signal Counter_Adr : STD_LOGIC; --0x8020

206

207 --Rear J4 Connector Address Decode Signals

```

and accompanying comments as indicated by the box to the right. This creates a new address strobe for our counter. It will be located in register 0x8020.

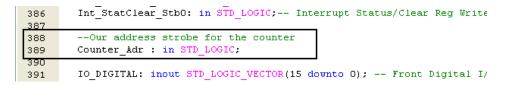

1. Open XC6SLX150.vhd and

scroll down to around line

**205**. Add the line of code

- 2. Around **line 388** insert these two lines of code to the declaration of the AXM\_D component. We will soon be changing the AXM\_D.vhd file to match this declaration.

- 3.Add the following around **line 765** our mapping of the Counter\_Adr strobe to the AXM\_D instantiation. Now the AXM\_D component will receive all the information it needs for the design.

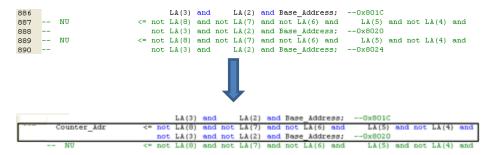

- 4. We will now replace a previously unused memory address. Uncomment line 928 and 929 and replace the "NU" with Counter\_Adr. This will be the location in memory to access the counter.

| 763 | <pre>Int_Polarity_Adr =&gt; Int_Polarity_Adr,</pre> |

|-----|-----------------------------------------------------|

| 764 |                                                     |

| 765 | Our address strobe                                  |

| 766 | Counter_Adr=> Counter_Adr,                          |

| 767 |                                                     |

| 768 | Write Stobes                                        |

|     |                                                     |

|     |                                                     |

5.To **line 992** add the code in the red box. This is added to strobe the AXM (where the rest of the counter code will be located) when the Counter\_Adr has received a read or write command.

We are finished editing the XC5VLX110T.vhd file and will now be **editing the AXM\_D.vhd** file.

- 6. After opening **AXM\_D.vhd**, scroll down to **line 31** and add the Counter\_Adr port. This is how the counter will be receiving the address strobe from the main vhdl code.

- 7.To **line 64** add the write strobe for the counter. This will pulse when a write command is issued the counter address.

- 8. At line 78 add the signals (registers) that the counter will be using. Counter\_EN will enable the counter, Counter\_Inc will determine if the counter is incrementing or not, and Counter\_Reg is the binary counter.

- 9.At around **line 231** we will insert the counter's write strobe. This will pulse **Counter\_Stb** when there is a write command to the **Counter\_Adr.**

990 991 AXM\_Strobe <= DiffReg31to0\_Adr or DigReg15to0\_Adr or DiffDirReg\_Adr or DigDirReg\_Adr or Int\_Enable\_Adr or Int\_Type\_Adr or Int\_Polarity\_Adr or Counter\_Adr; 992 993 29 Int Polarity Adr: in STD LOGIC; -- Interru 30 31 -- The Counter Register's Address Strobe 32 Counter Adr : in STD LOGIC; 33 34 Int StatClear Stb0: in STD LOGIC;-- Interru 62 signal Int Polarity Stb0 : STD LOGIC; 63 -- The Write Strobe signal for the Counter 64 signal Counter\_Stb : STD\_LOGIC; 65 66 67 -- Register Signals ------76 signal IOA: STD LOGIC VECTOR (7 downto 0); 77 78 -- The Counter's Signals 79 -- Enable the counter for use 80 signal Counter EN : STD LOGIC; 81 -- Increment the Counter by one 82 signal Counter Inc : STD LOGIC; 83 -- The Counter's Register 84 signal Counter\_Reg : STD\_LOGIC\_Vector(3 downto 0); 85 -- I/O component for detection of Change of State Ir 86 232 -- The Counter Register's Write Strobes 233 process (CLK) 234 begin if (CLK'event and CLK = '1') then 235 Counter Stb <= Counter Adr and not ADS n and 236 237 not LBEO n and LW R n; 238 end if: 239 end process;

--Interrupt Registers Write Strobes

240 241

- At line 350 there is the process statement to control the Differential Direction Control Register. Add the red code to cause channels 0-3 to become outputs when there is a write to the counter address, and make sure that channel 4 is an input to handle the increment line.

- Add this process statement at line 434 to handle the enable for the counter. Notice that Counter\_EN receives its information from the local data bus (LD) bit-5.

- Add this process statement at line 449 to handle the external increment line for the counter. Notice that the Counter\_Inc receives its information from channel 4. The counter is stopped and started using this input line.

- 13. Add this process statement at **line 464** to handle the counter. When the counter is enabled, it will check the Counter\_Inc line to see if it has a positive logic equivalence of '1' every positive clock edge. If it does then the counter will be incremented.

```

--Front I/O Differential Direction Control Register 0x8008

process (CLK, RESET)

begin

if (RESET = '1') then

DiffDir Reg(7 downto 0) <= "00000000";

elsif (CLK'event and CLK = '1') then

if (DiffDirReg_Stb0 = '1') then

DiffDir Reg(7 downto 0) <= LD(7 downto 0);

-- If there is a Counter_Stb pre-config the direction

-- to channel 4 as an input and channels 3-0 as outputs

elsif (Counter Stb = '1') then

DiffDir_Reg(7 downto 0) <= "00001111";

else

DiffDir Reg(7 downto 0) <= DiffDir_Reg(7 downto 0);</pre>

end if:

end if:

end process;

435

-- Counter EN Register 0x8020 bit 5

-- Turns on the functionality of the Counter

436

437

process (CLK, RESET)

438

begin

439

if (RESET = '1') then

Counter EN <= '0';

440

elsif (CLK'event and CLK = '1') then

441

442

if (Counter Stb = '1') then

443

Counter EN <= LD(5);

444

else

445

Counter EN <= Counter EN;

446

end if:

447

end if;

448

end process;

450

-- Counter Inc determine when to load the counter

451

-- Register 0x8020 bit 4

452

process (CLK, RESET)

begin

453

if (RESET = '1') then

454

455

Counter Inc <= '0';

elsif (CLK'event and CLK = '1') then

456

457

if (Counter EN = '1') then

458

Counter Inc <= IO DIGITAL(4);

459

else

460

Counter Inc <= Counter Inc;

461

end if;

462

end if;

463

end process;

465

-- Counter_Reg determine when to increment the counter

466

process (CLK, RESET)

467

begin

468

if (RESET = '1') then

Counter Reg <= "00000";

469

elsif (CLK'event and CLK = '1') then

470

471

if (Counter_EN = '1' and Counter_Inc = '1') then

472

Counter Reg <= Counter Reg + 1;

473

else

474

Counter_Reg <= Counter_Reg;

475

end if;

476

end if;

477

end process;

```

Add the following lines of red code to the READ\_DATA MUX. This will allow the read and write commands to access the counter address at 8020H.

Bits 3-0 will hold the four bits of the counter, bit 4 will hold the increment line, and bit 5 will hold the enable.

```

535

READ DATA(O) <=

536

(Counter Reg(0) and Counter Adr) or

537

(IO_DIFF(0) and DiffReg31to0_Adr) or

538

(IO DIGITAL(0) and DigReg15toO Adr) or

(DiffDir_Reg(0) and DiffDirReg_Adr) or

539

540

(DigDir_Reg(0) and DigDirReg_Adr) or

541

542

(IntEnA_Reg(0) and Int_Enable_Adr) or

(IntTyp& Reg(0) and Int_Type &dr) or

(IntPol& Reg(0) and Int_Polarity_&dr);

543

544

545

546

547

READ DATA(1) <=

548

(Counter_Reg(1) and Counter_Adr) or

549

(IO_DIFF(1) and DiffReg31to0_Adr) or

(IO DIGITAL(1) and DigReg15toO Adr) or

551

(DiffDir_Reg(1) and DiffDirReg_Adr) or

552

(DigDir_Reg(1) and DigDirReg_Adr) or

553

554

(IntEnA_Reg(1) and Int_Enable_Adr) or

555

(IntTypA Reg(1) and Int Type Adr) or

556

(IntPolA_Reg(1) and Int_Polarity_Adr);

559 READ_DATA(2) <=

(Counter_Reg(2) and Counter_Adr) or

560

(IO_DIFF(2) and DiffReg31to0_Adr) or

561

562

(IO DIGITAL(2) and DigReg15toO Adr) or

563

(DiffDir Reg(2) and DiffDirReg Adr) or

564

(DigDir_Reg(2) and DigDirReg_Adr) or

565

566

(IntEnA Reg(2) and Int Enable Adr) or

567

(IntTypA_Reg(2) and Int_Type_Adr) or

568

(IntPolk Reg(2) and Int Polarity &dr);

569

570

571

READ DATA(3) <=

572

(Counter_Reg(3) and Counter_Adr) or

573

(IO DIFF(3) and DiffReg31toO Adr) or

574

(IO DIGITAL(3) and DigReg15toO Adr) or

575

(DiffDir Reg(3) and DiffDirReg Adr) or

(DigDir_Reg(3) and DigDirReg_Adr) or

576

577

578

(IntEnA Reg(3) and Int Enable Adr) or

579

(IntTyp& Reg(3) and Int Type Adr) or

(IntPolA_Reg(3) and Int_Polarity_Adr);

580

READ_DATA(4) <=

583

584

(Counter_Inc and Counter_Adr) or

585

(IO DIFF(4) and DiffReg31toO Adr) or

586

(IO DIGITAL(4) and DigReg15toO Adr) or

587

(DiffDir Reg(4) and DiffDirReg_Adr) or

588

(DigDir_Reg(4) and DigDirReg_Adr) or

589

(IntEn&_Reg(4) and Int_Enable_&dr) or

590

591

(IntTypk Reg(4) and Int Type Adr) or

592

(IntPol& Reg(4) and Int Polarity Adr);

593

594

READ DATA(5) <=

595

(Counter_EN and Counter_Adr) or

596

(IO DIFF(5) and DiffReg31toO Adr) or

597

(IO DIGITAL(5) and DigReg15toO Adr) or

598

(DiffDir Reg(5) and DiffDirReg Adr) or

599

(DigDir_Reg(5) and DigDirReg_Adr) or

600

601

(IntEnA Reg(5) and Int Enable Adr) or

602

(IntTyp& Reg(5) and Int Type &dr) or

(IntPol& Reg(5) and Int Polarity Adr);

603

```

#### **Simulating the Example Design Using ISIM**

Xilinx ISE Design Suite provides an ISim simulator as a means to simulate designs. This tutorial will take you through the procedure for simulating the example design, reading and writing to the Dual-Port SRAM. We use a Dual-Port SRAM VHDL model provided by the Free Model Foundry.

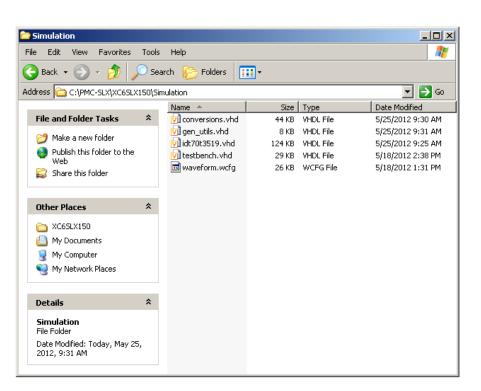

- 1. Make a new folder in the the previously created XC6SLX150 directory and call it **Simulation**.

- 2. From the Simulation folder, copy the .vhd file and the .wcfg file into the new Simulation folder.

- To obtain the DP-SRAM model go to <u>http://www.freemodelfound</u> <u>ry.com/ram.php</u> and download idt70t3519.vhd. Save it in the Simulation folder.

- 4. To get the library files for the model, go to <a href="http://www.freemodelfound">http://www.freemodelfound</a> <a href="http://www.freemodelfound">ry.com/packages.php</a> and <a href="http://www.freemodelfound">download conversions.vhd</a> and <a href="http://www.freemodelfound">gen/packages.php</a> and <a href="http://www.freemodelfound">download conversions.vhd</a> and <a href="http://www.freemodelfound">gen/packages.php</a> and <a href="http://www.freemodelfound">download conversions.vhd</a> and <a href="http://www.freemodelfound">gen\_utils.vhd</a>. Save them both in the Simulation folder. The Simulation folder should now contain all of the files shown in the adjacent screenshot.

- 5. For simulation with the DP-SRAM model we must create an empty file and call it **none** inside the SLX150 folder as shown in the screen shot to the right (This can not be a text file. No .txt extention.)

- Next we will add the files needed for simulation to the previously created project. Follow these steps:

- a. Select Project → Add Source.

- b. Select the .vhd files from the Simulation folder.

- c. Click Open.

- d. The association for all four files should be *Simulation*.

- e. Click the drop-down menu for Library to select *New VHDL Library*. The New VHDL Library window will open.

- f. Create the new library in the SLX150 folder and name it **FMF** as shown in the adjacent screenshot.

- g. Back in the Adding Source Files window, change the libraries for the .vhd file as shown in the screenshot on the right. Testbench.vhd should be the only one with library work.

- h. Click OK.

| FMF        C:\PMC-SLX\XC6SLX150\SLX150                                                                                                                                                                                                                                            |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                   |     |

| Adding Source Files                                                                                                                                                                                                                                                               |     |

| The following allows you to see the status of the source files being added to the project.<br>also allows you to specify the Design View association, and for VHDL sources the library, j                                                                                         | for |

|                                                                                                                                                                                                                                                                                   | for |

| also allows you to specify the Design View association, and for VHDL sources the library, sources which are successfully added to the project.           File Name         Association         Library                                                                            | for |

| also allows you to specify the Design View association, and for VHDL sources the library, sources which are successfully added to the project.           File Name         Association         Library           1         O idt70t3519.vhd         Simulation         Image: FMF |     |

| also allows you to specify the Design View association, and for VHDL sources the library, sources which are successfully added to the project.           File Name         Association         Library                                                                            |     |

800

801

802

803

- Next we need to edit conversion.vhd. Follow these steps:

- a. Click the Files tab.

- Resize the Columns to view the names of the files and double-click conversions.vhd to open it.

- Modify line 802 as shown in the screenshot to the right.

- d. Save and close conversions.vhd.

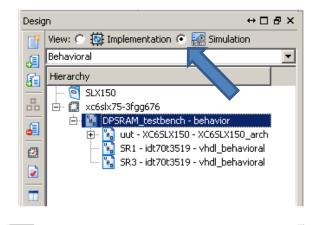

Select the **Design** tab.

- 8. Click the **Simulation** radio button for ISim.

- The design hierarchy for simulation should appear in the window as shown in the adjacent screenshot. Click on DPSRAM\_testbench behavior to highlight it.

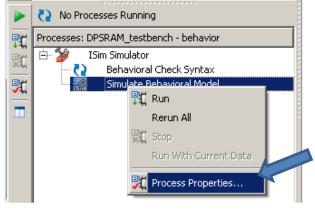

- 10. In the Processes Window, expand **ISim Simulator** and right-click *Simulate Behavioral Model*. Select *Process Properties*.

case int(i) is when '1' | 'H' => r := r + place; when '0' | 'L' | 'U' => null; when others =>

11. The Process Properties window will appear. Change the simulation run time to 3500 ns and check the Use Custom Waveform Configuration box. Browse to the file **waveform.wcfg** in the Simulation folder for the configuration file. Click OK.

| TOCCOSTITO | perties - ISim Properties              |                                                           |

|------------|----------------------------------------|-----------------------------------------------------------|

| witch Name | Property Name                          | Value                                                     |

|            | Use Custom Simulation Command File     |                                                           |

|            | Custom Simulation Command File         |                                                           |

|            | Run for Specified Time                 | <u> </u>                                                  |

|            | Simulation Run Time                    | 3500 ns                                                   |

|            | Waveform Database Filename             | C:\PMC-SLX\XC65LX150\SLX150\DPSRAM_testbench_isim_beh.wdb |

|            | Use Custom Waveform Configuration File | <u>v</u>                                                  |

|            | Custom Waveform Configuration File     | C:\PMC-SLX\XC6SLX150\Simulation\waveform.wcfg             |

|            | Specify Top Level Instance Names       | work.DPSRAM_testbench                                     |

| Load glbl  |                                        | <u>v</u>                                                  |

|            |                                        | OK Cancel Apply Help                                      |

|            |                                        | sses Running                                              |

|            | ***                                    | SRAM_testbench - behavior                                 |

|            | 🖳 🖻 🎽 🚬 ISir                           | m Simulator                                               |

|            | <u>C2</u>                              | Behavioral Check Syntax                                   |

|            | <b>7</b>                               | Simulate Behavioral Model                                 |

|            | <u> </u>                               |                                                           |

|            |                                        |                                                           |

|            |                                        |                                                           |

|            |                                        |                                                           |

|            |                                        |                                                           |

|            |                                        |                                                           |

- 12. Double-click Simulate Behavioral Model.

- 13. After the simulation is complete and the ISIM window has appeared, click the Zoom to Full View Button in the ISIM toolbar.

14. The waveforms are now expanded and should look like the screenshot below.Click on the waveforms and a cursor will appear.

#### Note:

The testbench.vhd file starting at line707 provides additional documentation of the stimulus provided to generate this simulation.

```

707

-- Stimulus process

708

白

stim proc: process

709

begin

710

-- hold reset state for 100 ns.

711

wait for 100 ns;

LRESET_n <= '1';</pre>

714

PinADS_n <= '1';</pre>

715

RdyACK_n <= '1';

716

717

¢

--Writing a logic '1' to bit 8 of the Software Reset and Status Register will

718

--select the on board 125MHz oscillator

719

wait until (FPGA_CLK'event and FPGA_CLK = '1');

wait until (FPGA_CLK'event and FPGA_CLK = '1');

721

LA <= "1000000000000000000000000"; --Software Reset and Status Register 0x8000

722

wait until (FPGA_CLK'event and FPGA_CLK = '1');

724

wait until (FPGA_CLK'event and FPGA_CLK = '1');

725

wait until (FPGA_CLK'event and FPGA_CLK = '1');

LW_R_n \ll 1'; --enable write

726

LD <= "0000000000000000000000000000000000";

728

729

wait until (FPGA CLK'event and FPGA CLK = '1');

wait until (FPGA_CLK'event and FPGA_CLK = '1');

731

wait until (FPGA_CLK'event and FPGA_CLK = '1');

734

PinADS_n <= '1';</pre>

735

736

--READYn must be driven low, on read/write cycle, by the programmable FPGA (U7)

¢

--and held low until RdyACK_n is driven low byt he PCI bus interface chip (U5)

738

wait until READYn = '0';

739

wait until (FPGA CLK'event and FPGA CLK = '1');

wait until (FPGA_CLK'event and FPGA_CLK = '1');

740

wait until (FPGA_CLK'event and FPGA_CLK = '1');

741

742

RdyACK n <= '0';

--signals the end of a read/write cycle

```

| <b>€</b>          |             |                 |         |          |        |        |        |        |        | 862.606 | ns     |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

|-------------------|-------------|-----------------|---------|----------|--------|--------|--------|--------|--------|---------|--------|----------|--------|---------|---------|---------|--------|--------|-----|--------|---------------------|--------|-------|-----------------|-------|-------|-----|-------|-------|------------|

| Name              |             | Value           | 0 ns    |          |        | 5      | 00 ns  |        |        |         | 1,000  | ns       |        |         | 1,500   | ns ,    |        |        | 2,  | 000 ns |                     |        |       | 2,500 n         | 5     |       |     | 3,000 | ns    |            |

| 省 🖓 քթ            | iga_dk 1    |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| 🚄 🕨 🐝 la          | [26:2] 1    | .00200£         | 0000000 | 1002     |        | . (100 | ) (100 | 20)(10 | 00200f | 10020   | . 1002 | :00f)(1) | 0 10   |         | 0020.   | . 10020 | 0f)(10 |        | Xto | J2)(   | 002                 | 1002   | 1002. | 1002.           |       |       |     | œ)(   | .002  | 100200F    |

| 🕓 🛛 🗓 рі          | inads_n 1   |                 |         |          | ſ      |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| 🕥 🛛 🔓 rd          | iyack_n 1   |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| 👍 🕛 te            |             |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     | T     |       |            |

| 🗻 🕹 ka            | 1 1.1       |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| 🚽 🕨 🐝 Id          | [31:0] £    | edcba98         | 000000  | JU (O    | 0)(80  | ))(þ   | 00 76  | 543)   | fedcb. | aaaaa   |        | 555)     | 00 ) 0 | 0 000.  | . a278t |         | 7)(    |        | )¢  | ))>    |                     | (X)    | XX.   | .) <u>X (</u> . | X     | X     | (X  | . 🗔 🕅 | X     |            |

| 🍈 🕨 式 sr          | _io[63:0] £ | edcba9876543210 | ZZZ     | 222222   | 222222 |        | 000    |        | )(fec  | cb)(fe  | dcb)   | 5555     | ZZZZZ  | ZZZZ (S | 55 ) 55 | 555X    | 56df   | 222222 | 222 | ZZZZ   | ) <mark>X</mark> ZZ | .z 💥 z | ZZ 💥  | zzz)            | ZZZ 💥 | 2222) | ZZZ | ZZZZ  | X ZZZ | X ZZZZZZZZ |

| 1 🔪 🕨 📷 sr        | _a[19:0] 0  | 0001            | 00000   | <u> </u> |        | 000    | 100    |        |        | 0000    | )i     | ) 0      | 0002   | X       | 00003   |         | 00     | 004 🗙  | 0   | 00000  |                     | 0000   |       | 000             | 02    | 00    | 003 | DC -  | 00004 | 00005      |

|                   | 1_r_wn 1    |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| 🕅 😼 sr            | 1_ceOn 1    |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| 20 16 5           | 1_oen 1     |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| 📻 🖌 🖉 sr          | 3_r_wn 1    |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

| line and a second | 3_ceOn 1    |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     | J     |       |            |

| lle sr            | 3_oen 1     |                 |         |          |        |        |        |        |        |         |        |          |        |         |         |         |        |        |     |        |                     |        |       |                 |       |       |     |       |       |            |

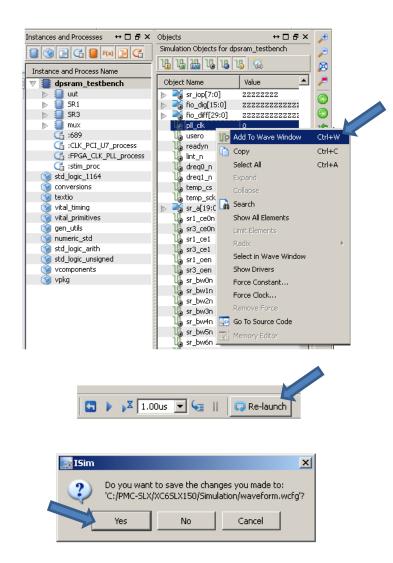

- 15. More objects can be added to the waveform window for simulation, for example, we will add the **pll\_clk** signal:

- a. In the *Instances and Processes* window, find the correct instance or process that the object belongs to and click on it to highlight it, in this case it is **dpsram\_testbench**.

- b. In the *Objects* window, find the object's name, **pll\_clk**, right-click the object, and select **Add to Wave Window**.

- c. The name of the object should now appear in the waveform window.

- d. Rerun the simulation; click **Re-launch** at the top of the ISIM window. Be sure to save the new waveform configuration file when prompted.

- e. After simulation is complete, the signal will appear in the waveform window. Signals can also be dragged and dropped to different locations within the waveform window.

### **Generating a Programming "MCS" File**

The Xilinx "MCS" contains the information to program the X6SLX150 through either FLASH or JTAG. These instructions will take you through the procedure for creating a MCS file.

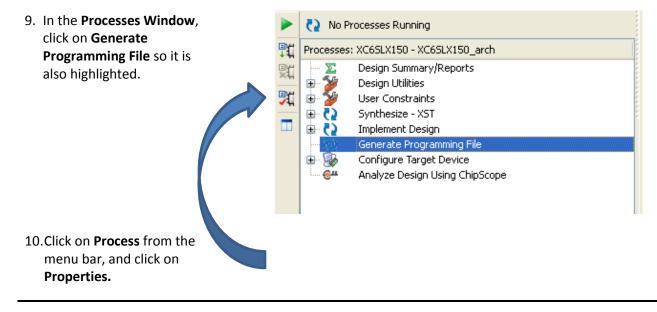

- Select XC6SLX150-XC6SLX150 \_arch (XC6SLX150.vhd) in the Hierarchy Window.

- Select Synthesize-XST in the Processes Window. Then select Process Properties and verify the setting shown in figure to right. Then select Process →Run.

**Note:** If there are any errors, correct them and repeat steps 1 and 2. There are 8 warnings.

| Processes | : XC6SLX150 - XC6SLX150_arch   |

|-----------|--------------------------------|

| <b>S</b>  | Design Summary/Reports         |

| 🗄 🤡       | Design Utilities               |

| 🗄 🛛 🎾     | User Constraints               |

| ± ₹2      | Synthesize - XST               |

| 🖻 🚺       | Implement Design               |

| - C2      | Generate Programming File      |

| 🖻 - 🕵     | Configure Target Device        |

| ен        | Analyze Design Using ChipScope |

|           |                                |

|           |                                |

| ategory                                                          | Switch Name               | Property Name                  | Value                                          |

|------------------------------------------------------------------|---------------------------|--------------------------------|------------------------------------------------|

| - Synthesis Options                                              | -opt_mode                 | Optimization Goal              | Speed                                          |

| <ul> <li>HDL Options</li> <li>Xilinx Specific Options</li> </ul> | -opt_level                | Optimization Effort            | Normal                                         |

| nan spoane options                                               | -power                    | Power Reduction                |                                                |

|                                                                  | -iuc                      | Use Synthesis Constraints File |                                                |

|                                                                  | -uc                       | Synthesis Constraints File     | [                                              |

|                                                                  | -keep_hierarchy           | Keep Hierarchy                 | Yes                                            |

|                                                                  | -netlist_hierarchy        | Netlist Hierarchy              | As Optimized                                   |

|                                                                  | -glob_opt                 | Global Optimization Goal       | AllClockNets                                   |

|                                                                  | -rtlview                  | Generate RTL Schematic         | Yes                                            |

|                                                                  | , -read_cores             | Read Cores                     |                                                |

|                                                                  | -sd                       | Cores Search Directories       |                                                |

|                                                                  | -write_timing_constraints | Write Timing Constraints       |                                                |

|                                                                  | -cross_clock_analysis     | Cross Clock Analysis           |                                                |

|                                                                  | -hierarchy_separator      | Hierarchy Separator            | 1                                              |

|                                                                  | -bus_delimiter            | Bus Delimiter                  | $\diamond$                                     |

|                                                                  | -slice_utilization_ratio  | LUT-FF Pairs Utilization Ratio | 100                                            |

|                                                                  | -bram_utilization_ratio   | BRAM Utilization Ratio         | 100                                            |

|                                                                  | -dsp_utilization_ratio    | DSP Utilization Ratio          | 100                                            |

|                                                                  | -case                     | Case                           | Maintain                                       |

|                                                                  |                           | Work Directory                 | \PMC-SLX150_RevB\X6SLX150_9000601\SLX150\xst ( |

|                                                                  | set -xsthdpini            | HDL INI File                   |                                                |

|                                                                  |                           | Library for Verilog Sources    |                                                |

|                                                                  | -lso                      | Library Search Order           |                                                |

|                                                                  | -vlgincdir                | Verilog Include Directories    | + .                                            |

|                                                                  | -generics                 | Generics, Parameters           |                                                |

|                                                                  | -define                   | Verilog Macros                 |                                                |

|                                                                  |                           | Other XST Command Line Options |                                                |

|                                                                  |                           | Property display level:        |                                                |

| ategory                                | Switch Name                 | Property Name               | Value                                              |  |  |

|----------------------------------------|-----------------------------|-----------------------------|----------------------------------------------------|--|--|

| Synthesis Options                      | -fsm_extract, -fsm_encoding | FSM Encoding Algorithm      | One-Hot                                            |  |  |

| HDL Options<br>Xilinx Specific Options | -safe_implementation        | Safe Implementation         | No                                                 |  |  |

| ·····                                  | -vldcase                    | Case Implementation Style   | None                                               |  |  |

|                                        | -fsm_style                  | FSM Style                   | LUT                                                |  |  |

|                                        | -ram_extract                | RAM Extraction              |                                                    |  |  |

|                                        | -ram_style                  | RAM Style                   | Auto                                               |  |  |

|                                        | -rom_extract                | ROM Extraction              |                                                    |  |  |

|                                        | -rom_style                  | ROM Style                   | Auto                                               |  |  |

|                                        | -auto_bram_packing          | Automatic BRAM Packing      |                                                    |  |  |

|                                        | -shreg_extract              | Shift Register Extraction   |                                                    |  |  |

|                                        | -shreg_min_size             | Shift Register Minimum Size | 2                                                  |  |  |

|                                        | -resource_sharing           | Resource Sharing            |                                                    |  |  |

|                                        | -use_dsp48                  | Use DSP Block               | Auto                                               |  |  |

|                                        | -async_to_sync              | Asynchronous To Synchronous |                                                    |  |  |

|                                        |                             |                             |                                                    |  |  |

|                                        |                             |                             |                                                    |  |  |

|                                        |                             | Property display level: Ad  | Ivanced 🔽 🗹 Display <u>s</u> witch names 🛛 Default |  |  |

| ategory                                                    | Switch Name                  | Property Name                    | Value                                     |

|------------------------------------------------------------|------------------------------|----------------------------------|-------------------------------------------|

| <ul> <li>Synthesis Options</li> <li>HDL Options</li> </ul> | -iobuf                       | Add I/O Buffers                  |                                           |

| Xilinx Specific Options                                    | -max_fanout                  | Max Fanout                       | 500000                                    |

|                                                            | -bufg                        | Number of Clock Buffers          | 32                                        |

|                                                            | -register_duplication        | Register Duplication             |                                           |

|                                                            | -equivalent_register_removal | Equivalent Register Removal      |                                           |

|                                                            | -register_balancing          | Register Balancing               | No                                        |

|                                                            | -move_first_stage            | Move First Flip-Flop Stage       |                                           |

|                                                            | -move_last_stage             | Move Last Flip-Flop Stage        |                                           |

|                                                            | -iob                         | Pack I/O Registers into IOBs     | Auto                                      |

|                                                            | -lc                          | LUT Combining                    | No                                        |

|                                                            | -reduce_control_sets         | Reduce Control Sets              | No                                        |

|                                                            | -use_clock_enable            | Use Clock Enable                 | Auto                                      |

|                                                            | -use_sync_set                | Use Synchronous Set              | Auto                                      |

|                                                            | -use_sync_reset              | Use Synchronous Reset            | Auto                                      |

|                                                            | -optimize_primitives         | Optimize Instantiated Primitives |                                           |

|                                                            |                              | Property display level: Adv      | ranced 🔽 🗹 Display switch names 🛛 Default |

- Select Implement Design in the Processes Window. Then select Process → Process Properties. Verify the settings shown in the figure to the right..

- 4. Select OK

- Select Implement Design in the Processes Window.

Then right mouse select Process → Run

- Note: Translate, Map, and Place and Route should complete with no errors and no additional warnings.

- Select XC6SLX150-XC6SLX150 \_arch (XC6SLX150.vhd) in the Hierarchy Window.

- Select Generate Programming File in the Processes Window. Then select Process →Run.

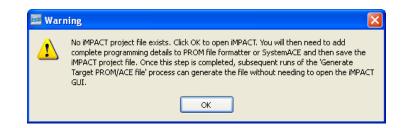

- Expand Configure Target Device and then Right-click on Generate Target PROM/ACE File, and click on Run.

Contractions - Section - S Category Switch Name Property Name Value Translate Properties Placer Effort Level -ol High ~ Map Properties -xe Placer Extra Effort None Y Place & Route Properties Post-Map Static Timing Report Prop Starting Placer Cost Table (1-100) \$ -t 1 Post-Place & Route Static Timing Re -xt Extra Cost Tables ~ Simulation Model Properties 0 -logic\_opt Combinatorial Logic Optimization -register\_duplication ~ Register Duplication Off Register Ordering 4 v -global opt Global Optimization Off ~ -equivalent\_register\_removal Equivalent Register Removal Ignore User Timing Constraints -ntd Timing Mode Performance Evaluation Trim Unconnected Signals -u -ignore\_keep\_hierarchy Allow Logic Optimization Across Hierarchy 📃 -detail Generate Detailed MAP Report Use RLOC Constraints × Yes Pack I/O Registers/Latches into IOBs Off ~ -pr Maximum Compression -lc LUT Combining Off ~ -bp Map Slice Logic into Unused Block RAMs -power Power Reduction Off v -activityfile Power Activity File Enable Multi-Threading -mt Off Other Map Command Line Options Property display level: Advanced 🔽 🗹 Display switch names Default < > OK Cancel Apply Help Design Summary/Reports Σ 1 Design Utilities € **N** ÷ User Constraints 🖶 🔁 🛋 Synthesize - XST Ė Implement Design - 62 Generate Programming File Configure Target Device ÷ 무는 œщ Analyze Design Using ChipScope Σ Design Summary/Reports 1 Design Utilities € ×5 ÷ User Constraints 😥 🍋 🛝 Synthesize - XST 🖻 🤁 🦺 Implement Design 🗄 🚺 🚺 Translate 🗄 🔁 🚺 Map 🖻 🔁 🛝 Place & Route 💫 🥼 Generate Programming File Configure Target Device Ē Generate Target PROM/ACE File Manage Configuration Project (iMPACT) <del>6</del>1 Analyze Design Using ChipScope

10. Select **OK**.

11. Double select Create PROM File (PROM File Formatter)

| iMPACT Flows ↔ 🗆 🗗 🗙                                                                                                |

|---------------------------------------------------------------------------------------------------------------------|

| Boundary Scan<br>SystemACE<br>Create PROM File (PROM File Formatter)<br>WebTalk Data<br>Double Click to Launch Mode |

|                                                                                                                     |

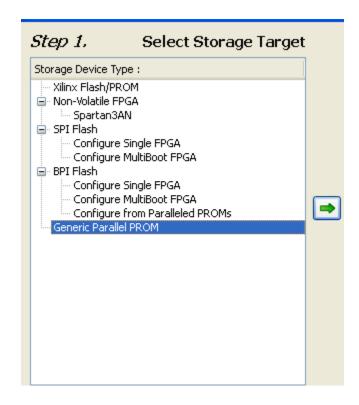

12. Select Generic Parallel **PROM** and the select the green arrow.

Select 8M and then select

Add Storage Device. Then select the next green arrow.

14. Verify the Output File location and enter an Output File Name. For example PSLX150. Leave all other default options and select **OK**.

| Step 3,                 |                               | Enter Dat | ta |  |  |  |  |

|-------------------------|-------------------------------|-----------|----|--|--|--|--|

| General File Detail     |                               | Value     |    |  |  |  |  |

| Checksum Fill<br>Value  | FF                            |           |    |  |  |  |  |

| Output File Name        | pslx150                       |           |    |  |  |  |  |

| Output File<br>Location | an_FPGA/PMC-SLX150/X6SLX150 📂 |           |    |  |  |  |  |

| Flash/PROM Fil          | Value                         |           |    |  |  |  |  |

| File Format             | MCS                           | ~         |    |  |  |  |  |

| Loading Direction       | UP                            | ~         |    |  |  |  |  |

| Number Of Revision      | 1                             | ~         |    |  |  |  |  |

| Revision 0 Start Ad     | 0                             |           |    |  |  |  |  |

| Add Non-Configura       | No 🔽                          |           |    |  |  |  |  |

|                         |                               |           |    |  |  |  |  |

#### 15. Click **OK**.

| 16. Select xc6slx150.bit file and                                                    | Add Device                                                                                                            |   |         | ? 🛛                    |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---|---------|------------------------|

| then click <b>Open</b> .                                                             | Look jn: 🔁 SLX150                                                                                                     | • | 🗢 🗈 💣 🎫 |                        |

|                                                                                      | My Recent<br>Documents<br>Documents<br>Docktop<br>Desktop                                                             |   |         |                        |

|                                                                                      | My Documents<br>My Computer                                                                                           |   |         |                        |

|                                                                                      | My Network<br>Places<br>Files of type: FPGA Bit Files (*.bit)                                                         |   | •       | <u>O</u> pen<br>Cancel |

| 17. Click <b>NO</b> .                                                                | Image: Add Device       Image: Would you like to add another device file to Revision: 0 ?         Image: Yes       No | • |         |                        |

| 18. Click <b>OK</b> .                                                                | Add Device      You have completed the device file entry     Click 'Ok' to continue      OK                           |   |         |                        |

| 19. Click <b>OK</b> again.                                                           |                                                                                                                       |   |         |                        |

| 20. In the left pane iMPACT<br>Process Windows Double<br>click <b>Generate File.</b> | iMPACT Processes     ↔ □       Available Operations are:        Image: Generate File                                  |   |         |                        |

If the process completed with no errors the *Generate Succeeded* message will be displayed.

Generate Succeeded

The PSLX150.mcs file now resides in the targeted directory. From here the file can be downloaded to FLASH or directly to the FPGA using Acromag's software demonstration program for Windows or Linux. The file can also be downloaded via JTAG via the AXM-EDK adapter board when used in conjunction with a compatible Xilinx download cable.

### Differences in VHDL between the XMC-SLX150 and the XMC-SLX150-1M

The Dual-Port SRAM on the XMC-SLX150-1M is four times the size as on the base model. The result is that all registers that manage or use the address of the SRAM must have two extra bits. The majority of these registers are defined via a constant declaration on line 93 of DP\_SRAM.vhd. The declaration is **constant addr\_max: integer := 19;** (or 17 for the base model). The registers affected are listed below.

| Register/Counter | Description                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------|

| DMA0_THRESHOLD   | Register corresponding to 0x8048.                                                                     |

| DMA1_THRESHOLD   | Register corresponding to 0x804C.                                                                     |

| DMA0_RESET       | Register corresponding to 0x8050.                                                                     |

| DMA1_RESET       | Register corresponding to 0x8054.                                                                     |

| SRAM_ADD_Count   | Counter with the current address of the SRAM. Can be set and read via 0x8038 & 0x803C.                |

| ADD_RESET_VALUE  | Counter that contains a reset value for the SRAM which could from either of the RESET registers above |

In addition, there are some minor changes to the read logic. All differences are shown on the following page. Please note that there are no differences in the top level *x6slx150.vhd* file.

#### DP\_SRAM.vhd for XMC-SLX150

#### DP\_SRAM.vhd for XMC-SLX150-1M

| C:\Design\Spartan6\EDK\XMC-SLX150\X6SLX150\DP_SRAM.vhd                                    | C:\Des                          | sign/Spartan6/EDK/XMC-SLX150-1M/X6SLX150/DP_SRAM.vhd      |

|-------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------|

| 93 constant addr max: integer := 17;                                                      | 93                              | constant addr max: integer := 19;                         |

| 738 ADD_RESET_VALUE(18) <= (SRAM_IntAdr_StbAll and LD(18                                  |                                 | ADD RESET VALUE(18) <= (SRAM IntAdr StbAll and LD(18)) or |

| 739 (DMA0_EVENT and SRAM_Reset0_EN and I                                                  | DMA0_RESET(18)) or 739          |                                                           |

| 740 (DMA1_EVENT and SRAM_Reset1_EN and I                                                  | DMA1_RESET(18)); 740            |                                                           |

| 741 ADD_RESET_VALUE(19) <= (SRAM_IntAdr_StbAll and LD(19)                                 | )) orrequired for -1M mdoel 741 | ADD_RESET_VALUE(19) <= (SRAM_IntAdr_StbAll and LD(19)) or |

| 742 (DMA0_EVENT and SRAM_Reset0_EN and I                                                  | DMA0_RESET(19)) or 742          |                                                           |

| 743 (DMA1_EVENT and SRAM_Reset1_EN and I                                                  | DMA1 RESET(19)); 743            | (DMA1_EVENT and SRAM_Reset1_EN and DMA1_RESET(19));       |

| 788 SRR_A(18) <= '0';remove for -1M model                                                 |                                 |                                                           |

| 789 SRR_A(19) <= '0';remove for -1M model                                                 |                                 |                                                           |

| 790                                                                                       |                                 | · · · · · · · · · · · · · · · · · · ·                     |