# AP500/AP520/AP521 AcroPack Serial Communication Module

# **USER'S MANUAL**

ACROMAG INCORPORATED 30765 South Wixom Road Wixom, MI 48393-2417 U.S.A.

> Tel: (248) 295-0310 Email: solutions@acromag.com

Copyright 2016, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice.

8501053E

# **Table of Contents**

| 1.0 | GE  | NERAL INFORMATION                                     | 5 |

|-----|-----|-------------------------------------------------------|---|

|     | 1.1 | Intended Audience                                     | 5 |

|     | 1.2 | Preface                                               | 5 |

|     |     | 1.2.1 Trademark, Trade Name and Copyright Information | 5 |

|     |     | 1.2.2 Class A Product Warning                         | 5 |

|     |     | 1.2.3 Environmental Protection Statement              | 5 |

|     | 1.3 | AcroPack Information – All Models                     | 6 |

|     |     | Figure 1.1 - AP500 Block Diagram                      | 6 |

|     |     | Figure 1.2 - AP520 Block Diagram                      | 6 |

|     |     | Figure 1.3 - AP521 Block Diagram                      | 6 |

|     |     | 1.3.1 Ordering Information                            | 7 |

|     |     | Table 1.1 Ordering Options                            | 7 |

|     |     | 1.3.2 Key Features                                    | 7 |

|     | 1.4 | Signal Interface Products                             | 8 |

|     | 1.5 | Software Support                                      | 8 |

|     |     | Windows®                                              | 8 |

|     |     | VxWorks®                                              | 8 |

|     |     | Linux®                                                | 8 |

|     | 1.6 | References                                            | 9 |

| 2.0 | PRE | PARATION FOR USE10                                    | ) |

|     | 2.1 | Unpacking and Inspecting10                            | 0 |

|     | 2.2 | Installation Considerations12                         | 1 |

|     | 2.3 | Board Configuration12                                 | 1 |

|     | 2.4 | Field I/O Connector                                   | 1 |

|     |     | Table 2.1 Field I/O Connector Pin Assignments         | 2 |

|     |     | Table 2.2 Field I/O 68 PinConnector Assignments       |   |

|     | 2.5 | RS-422/485 Termination (AP521 Only)18                 | 8 |

|     | 2.6 | Noise and Grounding Considerations18                  | 8 |

|     | 2.7 | Logic In     | iterface Connector                                                                        | 18 |

|-----|-----|--------------|-------------------------------------------------------------------------------------------|----|

|     |     |              | Table 2.3 Logic Interface Connections                                                     | 18 |

| 3.0 | PRO | OGRAM        | IMING INFORMATION                                                                         | 20 |

|     |     | <b>DOI 0</b> |                                                                                           |    |

|     | 3.1 | PCIe Co      | onfiguration Registers                                                                    |    |

|     |     |              | Table 3.1 PCI Configuration Registers                                                     | 21 |

|     | 3.2 | UART a       | nd Device Configuration Registers                                                         | 21 |

|     |     |              | Table 3.2 UART and Device Configuration Registers                                         | 22 |

|     |     |              | Table 3.3 Device Configuration Registers in Byte Alignment                                | 22 |

|     |     |              | Table 3.4 Device Configuration Registers in DWORD Alignment                               |    |

|     |     | 3.2.1        | The Global Interrupt Registers – INTO, INT1, INT2 and INT3                                | 24 |

|     |     |              | Table 3.5 UART Channel Interrupt Source Encoding                                          | 24 |

|     |     | 3.2.1.       | 1 Interrupt Clearing                                                                      | 25 |

|     |     | 3.2.2        | General Purpose 16-bit Timer/Counter [TimerMSB, TimerLSB, TIMER, TIMECNTL]                | 25 |

|     |     |              | 3.2.2.1 TIMERMSB[31:24] and TIMERLSB[23:16]                                               | 25 |

|     |     |              | 3.2.2.2 TIMERCNTL[7:0] Register                                                           | 25 |

|     |     |              | Table 3.6 Timer Control Register                                                          | 26 |

|     |     |              | 3.2.2.3 Timer Operation                                                                   | 26 |

|     |     | 3.2.3        | 8XMODE[7:0] (default 0x00)                                                                | 28 |

|     |     | 3.2.4        | 4XMODE[15:8] (default 0x00)                                                               | 28 |

|     |     | 3.2.5        | RESET[23:16] (default 0x00)                                                               | 28 |

|     |     | 3.2.6        | SLEEP[31:24] (default 0x00)                                                               | 28 |

|     |     | 3.2.7        | DVID[15:8]                                                                                | 29 |

|     |     | 3.2.8        | DREV[7:0]                                                                                 | 29 |

|     |     | 3.2.9        | REGB[23:16] (default 0x00)                                                                | 29 |

|     |     |              | Table 3.7 REGB Register                                                                   | 29 |

|     |     | 3.2.10       | O MPIO Registers                                                                          | 30 |

|     | 3.3 |              | iit and Receive Data                                                                      |    |

|     |     |              | FIFO Data Loading and Unloading in 32-bit Format                                          |    |

|     |     |              | FIFO Data Loading/Unloading Through the UART Channel Registers, THR and RHR, in 8-E<br>at |    |

|     | 3.4 | UART C       | Channel Configuration Registers                                                           | 31 |

|     |     |              | Table 3.8 UART Channel Configuration Registers                                            | 31 |

|     |     | 3.4.1        | Receiver                                                                                  | 32 |

|     |     | 3.4.2        | Transmitter                                                                               |    |

|     |     |              | 3.4.2.1 Transmit Holding Register (THR)                                                   | 33 |

|     |     |              | 3.4.2.2 Transmitter Operation in non-FIFO mode                                            | 33 |

|     |     |              | 3.4.2.3 Transmitter Operation in FIFO mode                                                | 33 |

|     |     |              | 3.4.2.4 Auto RS485 Operation (AP521 Only)                                                 | 33 |

|     |     | 3.4.3        | Baud Rate Generator Divisors (DLM, DLL and DLD)                                           | 34 |

|     |     |              | 3.4.3.1 DLM[7:0], DLL[7:0] and DLD[3:0]                                                   | 34 |

|     |           | Table 3.9 Typical Data Rates with Internal 125MHz Clock at 16X Sampling                | 35 |

|-----|-----------|----------------------------------------------------------------------------------------|----|

|     |           | 3.4.3.2 DLD[7:4]                                                                       | 35 |

|     |           | Table 3.10 DLD Register[7:4]                                                           | 35 |

|     | 3.4.4     | Interrupt Enable Register (IER) – Read/Write                                           | 36 |

|     |           | 3.4.4.1 IER versus Receive FIFO Interrupt Mode Operation                               | 36 |

|     |           | 3.4.4.2 IER versus Receive/Transmit FIFO Polled Mode Operation                         | 36 |

|     |           | Table 3.11 Interrupt Enable Register                                                   | 36 |

|     | 3.4.5     | Interrupt Status Register (ISR) – Read Only                                            | 38 |

|     |           | 3.4.5.1 Interrupt Generation                                                           | 38 |

|     |           | 3.4.5.2 Interrupt Clearing                                                             | 39 |

|     |           | Table 3.12 Interrupt Source and Priority Level                                         | 39 |

|     | 3.4.6     | FIFO Control Register (FCR) – Write Only                                               | 40 |

|     |           | Table 3.13 FIFO Control Register                                                       | 40 |

|     |           | Table 3.14 Transmit and Receive FIFO Trigger Table and Level Selection                 | 41 |

|     | 3.4.7     | Line Control Register (LCR) – Read/Write                                               | 42 |

|     |           | Table 3.15 Line Control Register                                                       | 42 |

|     | 3.4.8     | Modem Control Register (MCR) – Read/Write                                              | 43 |

|     |           | Table 3.16 Modem Control Register                                                      | 43 |

|     | 3.4.9     | Line Status Register (LSR) – Read Only                                                 | 44 |

|     |           | Table 3.17 Line Status Register                                                        | 44 |

|     | 3.4.10    | Modem Status Register (MSR) – Read Only                                                | 46 |

|     |           | Table 3.18 Modem Status Register                                                       | 46 |

|     | 3.4.11    | Modem Status Register (MSR) – Write Only                                               | 47 |

|     |           | MSR [7:4]: Auto RS485 Turn-Around Delay (requires EFR bit [4]=1) (For use on the AP521 |    |

|     |           |                                                                                        |    |

|     |           | Table 3.19 Auto RS485 Half-Duplex Direction Control Delay from Transmit to Receive     |    |

|     |           | MSR[3:0]                                                                               |    |

|     |           | Table 3.20 MSR[3:0]                                                                    |    |

|     |           | Scratch Pad (SCR) – Read/Write                                                         |    |

|     | 3.4.13    | Feature Control Register (FCTR) – Read/Write                                           |    |

|     |           | Table 3.21 FCTR – Feature Control Register                                             |    |

|     | 3.4.14    | Enhanced Feature Register (EFR) – Read/Write                                           |    |

|     |           | Table 3.21 EFR - Enhanced Feature Register                                             |    |

|     |           | Transmit FIFO Level Counter – Read Only                                                |    |

|     |           | Transmit FIFO Trigger Level – Write Only                                               |    |

|     |           | Receive FIFO Level Counter – Read Only                                                 |    |

|     |           | Receive FIFO Trigger Level – Write Only                                                |    |

|     |           | XOFF1, XOFF2, XON1 and XON2 Registers – Write Only                                     |    |

|     | 3.4.20    | XCHAR Register – Read Only                                                             |    |

|     |           | Table 3.22 XCHAR Register                                                              | 53 |

| 4.0 | SERVICE A | ND REPAIR                                                                              | 55 |

| 4.1 | Service and Repair Assistance | 55 | 5 |

|-----|-------------------------------|----|---|

|-----|-------------------------------|----|---|

|     | 4.2  | Preliminary Service Procedure          | 55 |

|-----|------|----------------------------------------|----|

|     | 4.3  | Where to Get Help                      | 55 |

| 5.0 | SPE  | CIFICATIONS                            | 56 |

|     | 5.1  | Physical                               | 56 |

|     | 5.2  | Power Requirements                     | 56 |

|     |      | Table 5.1 Power Requirements           | 56 |

|     | 5.3  | Environmental Considerations           | 56 |

|     |      | 5.3.1 Operating Temperature            |    |

|     |      | 5.3.2 Other Environmental Requirements |    |

|     |      | 5.3.2.1 Relative Humidity              |    |

|     |      | 5.3.2.2 Isolation                      |    |

|     |      | 5.3.3 Vibration and Shock Standards    |    |

|     |      | 5.3.4 EMC Directives                   |    |

|     |      |                                        |    |

|     | 5.4  | Reliability Prediction                 | 57 |

|     |      | -<br>Table 5.4 MTBF (all models)       |    |

|     | 5.5  | PCIe Bus Specifications                | 58 |

| APP | END  | DIX A                                  | 59 |

|     | AP-  | CC-01 Heatsink Kit Installation        | 59 |

| CER | TIFI | CATE OF VOLATILITY                     |    |

| REV | ISIO | N HISTORY                              | 63 |

# **1.0 GENERAL INFORMATION**

### **1.1 Intended Audience**

This user's manual was written for technically qualified personnel who will be working with I/O devices using the AcroPack module. It is not intended for a general, non-technical audience that is unfamiliar with AcroPack devices and their application.

## **1.2 Preface**

The information contained in this manual is subject to change without notice, and Acromag, Inc. (Acromag) does not guarantee its accuracy. Acromag makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Further, Acromag assumes no responsibility for any errors that may appear in this manual and makes no commitment to update, or keep current, the information contained in this manual. No part of this manual may be copied or reproduced in any form, without the prior written consent of Acromag.

#### 1.2.1 Trademark, Trade Name and Copyright Information

© 2016 by Acromag Incorporated.

All rights reserved. Acromag and Xembedded are registered trademarks of Acromag Incorporated. All other trademarks, registered trademarks, trade names, and service marks are the property of their respective owners.

#### 1.2.2 Class A Product Warning

This is a Class A product. In a domestic environment this product may cause radio interference, in which case the user may find it necessary to take adequate corrective measures.

#### **1.2.3 Environmental Protection Statement**

This product has been manufactured to satisfy environmental protection requirements where possible. Many components used (structural parts, circuit boards, connectors, etc.) are capable of being recycled. Final disposition of this product after its service life must be conducted in accordance with applicable country, state, or local laws or regulations.

## **1.3** AcroPack Information – All Models

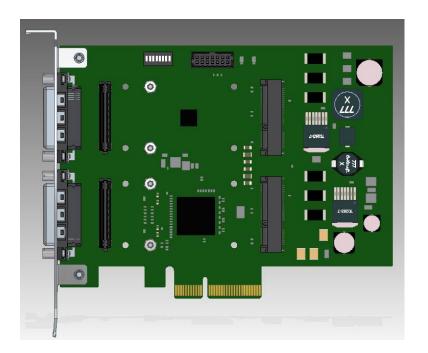

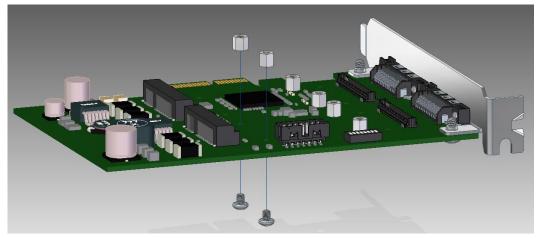

The AcroPack IO modules are based on the PCI Express Mini Card Electromechanical specification and are 70mm in length with an additional 100 pin field I/O connector.

The AcroPack is 19.05mm longer than the full length mini PCIe card at 50.95mm. It has the same mPCIe board width of 30mm and uses the same mPCIe standard board hold down standoff and screw keep out areas.

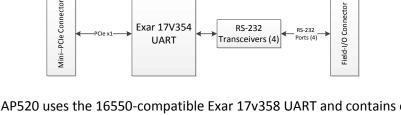

The AP500 uses the 16550-compatible Exar 17v354 UART and contains four RS-232 serial communication ports that provide full EIA/TIA-232E modem line support, including RTS, CTS, DTR, DSR, DCD, and RI.

#### Figure 1.1 - AP500 Block Diagram

RS-232

RS-232

Transceivers (8)

RS-232

RS-232

Ports (8

Field-I/O Connector

Exar 17V354

Exar 17V358

UART

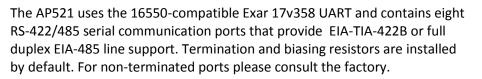

The AP520 uses the 16550-compatible Exar 17v358 UART and contains eight RS-232 serial communication ports that provide EIA/TIA-232E modem line support, including RTS, and CTS.

#### Figure 1.2 - AP520 Block Diagram

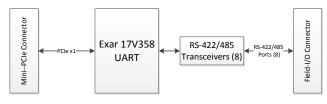

Figure 1.3 - AP521 Block Diagram

Mini--PCle Connector

#### 1.3.1 Ordering Information

#### Table 1.1 Ordering Options

The AcroPack ordering options are given in the following table.

| Model Number                | #/Type of<br>Serial Ports | Operational Temperature<br>Range |

|-----------------------------|---------------------------|----------------------------------|

| AP500E-LF <sup>1,2</sup>    | 4x RS-232                 | -40°C to 85°C <sup>1,2</sup>     |

| AP520-64E-LF <sup>1,2</sup> | 8x RS-232                 | -40°C to 85°C <sup>1,2</sup>     |

| AP521-64E-LF <sup>1,2</sup> | 8x RS-422/485             | -40°C to 85°C <sup>1,2</sup>     |

**Note 1**: For all models *listed - all standoffs and screws required for an air cooled application are provided with the carrier.*

**Note 2**: A conduction cooled application will require purchase of AcroPack Accessory **AP-CC-01** (Conduction Cool Kit).

#### **1.3.2** Key Features

- **High Density** Provides 4 (AP500) or 8 (AP520/521) serial ports on each module.

- **16550 compatible** Exar Quad or Octal UART with 16550-compatible register set.

- **256-Byte FIFO Buffers** 256-byte TX and RX FIFOs with programmable trigger levels.

- Programmable Baud Rate Each individual channel has its own programmable baud rate generator with fractional divisor. While the UART supports data rates up to 31.25Mbps, the serial transceivers only support data rates up to 500kbps (AP500/520) or 20Mbps (AP521).

- Interrupt Support Individually controlled transmit, receive, line status, and data set interrupts may be generated.

- General Purpose Timer/Counter This 16-bit timer/counter uses an internal 125MHz clock as the clock source and can be set to be a single-shot or re-triggerable and is capable of generating an interrupt.

- Individual Modem Control Signals The AP500 module provides all modem control signals: RTS, CTS, DTR, DSR, CD, and RI. The AP520 only provides RTS and CTS.

- PCle Bus The AP module includes a PCI Express Generation 1 interface operating at a bus speed of 2.5 Gbps with one lane in each direction.

• **Compatibility** – PCI Express Base Specification v2.0 compliant PCI Express Endpoint.

#### **1.4 Signal Interface Products**

This AcroPack module will mate directly to all Acromag AP carriers. Once connected, the module is accessed via a front panel connector.

The cables and termination panels are also available. For optimum performance with the AP5XX communication modules, use of the shortest possible length of shielded I/O cable is recommended.

#### **1.5 Software Support**

The AcroPack series products require support drivers specific to your operating system. Supported operating systems include: Linux, Windows, and VxWorks.

Windows® Acromag provides software products (sold separately) to facilitate the development of Windows® applications interfacing with AcroPack modules, VPX I/O board products, and PCIe I/O Cards. This software (model APSW-API-WIN) consists of low-level drivers and Dynamic Link Libraries (DLLs) that are compatible with a number of programming environments. The DLL functions provide a high-level interface to boards eliminating the need to perform low-level reads/writes of registers, and the writing of interrupt handlers.

VxWorks® Acromag provides a software product (sold separately) consisting of VxWorks® software. This software (Model APSW-API-VXW) is composed of VxWorks® (real time operating system) libraries for all AcroPack modules, VPX I/O board products, and PCIe I/O Cards. The software is implemented as a library of "C" functions which link with existing user code to make possible simple control of all Acromag AcroPack modules.

Linux® Acromag provides a software product consisting of Linux® software. This software (Model APSW-API-LNX) is composed of Linux® libraries for all AcroPack modules, VPX I/O board products, and PCIe I/O Cards. The software is implemented as a library of "C" functions which link with existing user code to make possible simple control of all Acromag AcroPack modules.

## **1.6 References**

The following resources regarding AcroPack modules are available for download on Acromag's website or by contacting your sales representative.

- PCI Express MINI Card Electromechanical Specification, REV 1.2 <u>http://www.pcisig.com</u>

- Exar 17v354 High Performance Quad PCI Express UART datasheet

- Exar 17v358 High Performance Octal PCI Express UART datasheet

# 2.0 PREPARATION FOR USE

# **IMPORTANT PERSONAL AND PRODUCT SAFETY CONSIDERATIONS**

It is very important for the user to consider the possible safety implications of power, wiring, component, sensor, or software failures in designing any type of control or monitoring system. This is especially important where personal injury or the loss of economic property or human life is possible. It is important that the user employ satisfactory overall system design. It is understood and agreed by the Buyer and Acromag that this is the Buyer's responsibility.

WARNING: This board utilizes static sensitive components and should only be handled at a static-safe workstation. This product is an electrostatic sensitive device and is packaged accordingly. Do not open or handle this product except at an electrostatic-free workstation. Additionally, do not ship or store this product near strong electrostatic, electromagnetic, magnetic, or radioactive fields unless the device is contained within its original manufacturer's packaging. Be aware that failure to comply with these guidelines will void the Acromag Limited Warranty.

## 2.1 Unpacking and Inspecting

Upon receipt of this product, inspect the shipping carton for evidence of mishandling during transit. If the shipping carton is badly damaged or water stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is absent when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, refer to the Acromag Service Policy to obtain return instructions. It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

This board is physically protected with packing material and electrically protected with an anti-static bag during shipment. However, it is recommended that the board be visually inspected for evidence of mishandling prior to applying power.

The board utilizes static-sensitive components and should only be handled at a static-safe workstation.

## **2.2 Installation Considerations**

| IMPORTANT: Adequate air<br>circulation must be provided to<br>prevent a temperature rise | Refer to the specifications section for loading and power requirements. Be<br>sure that the system power supplies are able to accommodate the power<br>requirements of the system boards, plus the installed Acromag board,<br>within the voltage tolerances specified.                                                                                       |  |  |  |  |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| above the maximum operating temperature.                                                 | In an air cooled assembly, adequate air circulation must be provided to<br>prevent a temperature rise above the maximum operating temperature and<br>to prolong the life of the electronics. If the installation is in an industrial<br>environment and the board is exposed to environmental air, careful<br>consideration should be given to air-filtering. |  |  |  |  |

|                                                                                          | In a conduction cooled assembly, adequate thermal conduction must be provided to prevent a temperature rise above the maximum operating temperature.                                                                                                                                                                                                          |  |  |  |  |

| 2.3 Board Configuration                                                                  |                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                                                                                          | Power should be removed from the board when installing AP modules,                                                                                                                                                                                                                                                                                            |  |  |  |  |

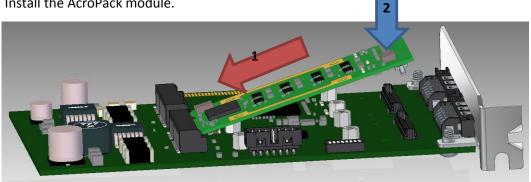

Power should be removed from the board when installing AP modules, cables, termination panels, and field wiring. Model AP500/520/521 UART communication boards have no hardware jumpers or switches to configure.

## 2.4 Field I/O Connector

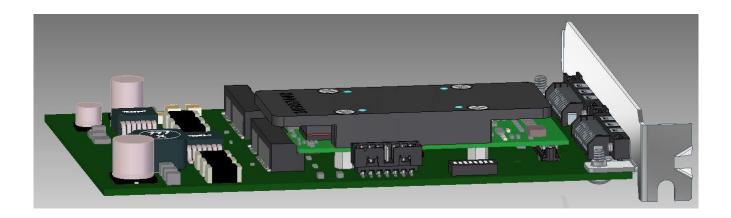

A field I/O interface connector provides a mating interface between the AP modules and the carrier board. The 100 pin ST5-50-1.50-L-D-P-TR Samtec connector is used on the AcroPack module as board to board interconnect. This connector will mate with the 100 pin SS5-50-3.00-L-D-K-TR Samtec connector on the carrier. The stack height is 4.5mm.

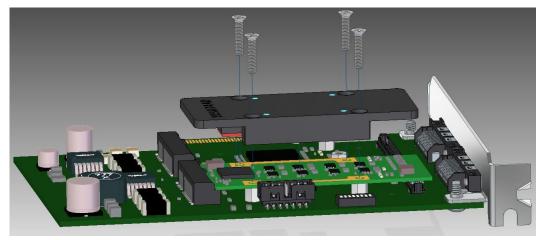

Threaded metric M2.5 screws and spacers are supplied with the module to provide additional stability for harsh environments.

Pin assignments are unique to each AP5XX model. <u>Table 2.1</u> lists signal pin assignments for the 100-pin module/carrier field I/O connectors, as well as the 50-pin and 68-pin CHAMP and ribbon I/O connectors on the carrier.

## Table 2.1 Field I/O Connector Pin Assignments

| 2.1 Field I/O Conne<br>Module/Carrier<br>Field I/O<br>Connector Pin # | Generic<br>Field I/O<br>Connector<br>Pin Name | Carrier 50-pin<br>Ribbon I/O<br>Connector<br>Pin# | Carrier 50-pin<br>CHAMP I/O<br>Connector<br>Pin# | AP500<br>Module<br>Function | AP520<br>Module<br>Function | AP521<br>Module<br>Function |

|-----------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------|--------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| 2                                                                     | Field I/O 1                                   | 1                                                 | 1                                                | GND                         | GND                         | GND                         |

| 1                                                                     | Field I/O 2                                   | 2                                                 | 26                                               | RI_A*                       | TXD_A                       | TXDA                        |

| 4                                                                     | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 3                                                                     | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 6                                                                     | Field I/O 3                                   | 3                                                 | 2                                                | DTR_A*                      | RXD_A                       | TXD+_A                      |

| 5                                                                     | Field I/O 4                                   | 4                                                 | 27                                               | CTS_A*                      | RTS_A*                      | RXDA                        |

| 8                                                                     | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 7                                                                     | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 10                                                                    | Field I/O 5                                   | 5                                                 | 3                                                | TXD_A                       | CTS_A*                      | RXD+_A                      |

| 9                                                                     | Field I/O 6                                   | 6                                                 | 28                                               | RTS_A*                      | GND                         | GND                         |

| 12                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 11                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 14                                                                    | Field I/O 7                                   | 7                                                 | 4                                                | RXD_A                       | TXD_B                       | TXDB                        |

| 13                                                                    | Field I/O 8                                   | 8                                                 | 29                                               | DSR_A*                      | RXD_B                       | TXD+_B                      |

| 16                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 15                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 18                                                                    | Field I/O 9                                   | 9                                                 | 5                                                | DCD_A*                      | RTS_B*                      | RXDB                        |

| 17                                                                    | Field I/O 10                                  | 10                                                | 30                                               | GND                         | CTS_B*                      | RXD+_B                      |

| 20                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 19                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 22                                                                    | Field I/O 11                                  | 11                                                | 6                                                | RI_B*                       | GND                         | GND                         |

| 21                                                                    | Field I/O 12                                  | 12                                                | 31                                               | DTR_B*                      | TXD_C                       | TXDC                        |

| 24                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 23                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 26                                                                    | Field I/O 13                                  | 13                                                | 7                                                | CTS_B*                      | RXD_C                       | TXD+_C                      |

| 25                                                                    | Field I/O 14                                  | 14                                                | 32                                               | TXD_B                       | RTS_C*                      | RXDC                        |

| 28                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 27                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 30                                                                    | Field I/O 15                                  | 15                                                | 8                                                | RTS_B*                      | CTS_C*                      | RXD+_C                      |

| 29                                                                    | Field I/O 16                                  | 16                                                | 33                                               | RXD_B                       | GND                         | GND                         |

| 32                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 31                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 34                                                                    | Field I/O 17                                  | 17                                                | 9                                                | DSR_B*                      | TXD_D                       | TXDD                        |

| 33                                                                    | Field I/O 18                                  | 18                                                | 34                                               | DCD_B*                      | RXD_D                       | TXD+_D                      |

| 36                                                                    | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| Module/Carrier<br>Field I/O<br>Connector Pin # | Generic<br>Field I/O<br>Connector<br>Pin Name | Carrier 50-pin<br>Ribbon I/O<br>Connector<br>Pin# | Carrier 50-pin<br>CHAMP I/O<br>Connector<br>Pin# | AP500<br>Module<br>Function | AP520<br>Module<br>Function | AP521<br>Module<br>Function |

|------------------------------------------------|-----------------------------------------------|---------------------------------------------------|--------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| 35                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 38                                             | Field I/O 19                                  | 19                                                | 10                                               | GND                         | RTS_D*                      | RXDD                        |

| 37                                             | Field I/O 20                                  | 20                                                | 35                                               | GND                         | CTS_D*                      | RXD+_D                      |

| 40                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 39                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 42                                             | Field I/O 21                                  | 21                                                | 11                                               | GND                         | GND                         | GND                         |

| 41                                             | Field I/O 22                                  | 22                                                | 36                                               | GND                         | TXD_E                       | TXDE                        |

| 44                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 43                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 46                                             | Field I/O 23                                  | 23                                                | 12                                               | GND                         | RXD_E                       | TXD+_E                      |

| 45                                             | Field I/O 24                                  | 24                                                | 37                                               | GND                         | RTS_E*                      | RXDE                        |

| 48                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 47                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 50                                             | Field I/O 25                                  | 25                                                | 13                                               | GND                         | CTS_E*                      | RXD+_E                      |

| 49                                             | Field I/O 26                                  | 26                                                | 38                                               | GND                         | GND                         | GND                         |

| 52                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 51                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 54                                             | Field I/O 27                                  | 27                                                | 14                                               | RI_C*                       | TXD_F                       | TXDF                        |

| 53                                             | Field I/O 28                                  | 28                                                | 39                                               | DTR_C*                      | RXD_F                       | TXD+_F                      |

| 56                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 55                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 58                                             | Field I/O 29                                  | 29                                                | 15                                               | CTS_C*                      | RTS_F*                      | RXDF                        |

| 57                                             | Field I/O 30                                  | 30                                                | 40                                               | TXD_C                       | CTS_F*                      | RXD+_F                      |

| 60                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 59                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 62                                             | Field I/O 31                                  | 31                                                | 16                                               | RTS_C*                      | GND                         | GND                         |

| 61                                             | Field I/O 32                                  | 32                                                | 41                                               | RXD_C                       | TXD_G                       | TXDG                        |

| 64                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 63                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 66                                             | Field I/O 33                                  | 33                                                | 17                                               | DSR_C*                      | RXD_G                       | TXD+_G                      |

| 65                                             | Field I/O 34                                  | 34                                                | 42                                               | DCD_C*                      | RTS_G*                      | RXDG                        |

| 68                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 67                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 70                                             | Field I/O 35                                  | 35                                                | 18                                               | GND                         | CTS_G*                      | RXD+_G                      |

| 69                                             | Field I/O 36                                  | 36                                                | 43                                               | RI_D*                       | GND                         | GND                         |

| Module/Carrier<br>Field I/O<br>Connector Pin # | Generic<br>Field I/O<br>Connector<br>Pin Name | Carrier 50-pin<br>Ribbon I/O<br>Connector<br>Pin# | Carrier 50-pin<br>CHAMP I/O<br>Connector<br>Pin# | AP500<br>Module<br>Function | AP520<br>Module<br>Function | AP521<br>Module<br>Function |

|------------------------------------------------|-----------------------------------------------|---------------------------------------------------|--------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| 72                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 71                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 74                                             | Field I/O 37                                  | 37                                                | 19                                               | DTR_D*                      | TXD_H                       | TXDH                        |

| 73                                             | Field I/O 38                                  | 38                                                | 44                                               | CTS_D*                      | RXD_H                       | TXD+_H                      |

| 76                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 75                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 78                                             | Field I/O 39                                  | 39                                                | 20                                               | TXD_D                       | RTS_H*                      | RXDH                        |

| 77                                             | Field I/O 40                                  | 40                                                | 45                                               | RTS_D*                      | CTS_H*                      | RXD+_H                      |

| 80                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 79                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 82                                             | Field I/O 41                                  | 41                                                | 21                                               | RXD_D                       | GND                         | GND                         |

| 81                                             | Field I/O 42                                  | 42                                                | 46                                               | DSR_D*                      | GND                         | No Connect                  |

| 84                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 83                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 86                                             | Field I/O 43                                  | 43                                                | 22                                               | DCD_D*                      | GND                         | No Connect                  |

| 85                                             | Field I/O 44                                  | 44                                                | 47                                               | GND                         | GND                         | No Connect                  |

| 88                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 87                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 90                                             | Field I/O 45                                  | 45                                                | 23                                               | GND                         | GND                         | No Connect                  |

| 89                                             | Field I/O 46                                  | 46                                                | 48                                               | GND                         | GND                         | No Connect                  |

| 92                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 91                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 94                                             | Field I/O 47                                  | 47                                                | 24                                               | GND                         | GND                         | No Connect                  |

| 93                                             | Field I/O 48                                  | 48                                                | 49                                               | GND                         | GND                         | No Connect                  |

| 96                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 95                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 98                                             | Field I/O 49                                  | 49                                                | 25                                               | GND                         | GND                         | No Connect                  |

| 97                                             | Field I/O 50                                  | 50                                                | 50                                               | GND                         | GND                         | No Connect                  |

| 100                                            | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

| 99                                             | RSVD/ISOL                                     |                                                   |                                                  |                             |                             |                             |

Note: An Asterisk (\*) is used to indicate an active-low signal.

| Module/Carrier<br>Field I/O<br>Connector Pin # | Generic<br>Field I/O<br>Connector<br>Pin Name | Carrier 68-pin CHAMP I/O<br>Connector Pin# | AP500<br>Module<br>Function | AP520<br>Module<br>Function | AP521<br>Module<br>Function |

|------------------------------------------------|-----------------------------------------------|--------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| 2                                              | Field I/O 1                                   | 1                                          | GND                         | GND                         | GND                         |

| 1                                              | Field I/O 2                                   | 35                                         | RI_A*                       | TXD_A                       | TXDA                        |

| 4                                              | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 3                                              | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 6                                              | Field I/O 3                                   | 2                                          | DTR_A*                      | RXD_A                       | TXD+_A                      |

| 5                                              | Field I/O 4                                   | 36                                         | CTS_A*                      | RTS_A*                      | RXDA                        |

| 8                                              | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 7                                              | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 10                                             | Field I/O 5                                   | 3                                          | TXD_A                       | CTS_A*                      | RXD+_A                      |

| 9                                              | Field I/O 6                                   | 37                                         | RTS_A*                      | GND                         | GND                         |

| 12                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 11                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 14                                             | Field I/O 7                                   | 4                                          | RXD_A                       | TXD_B                       | TXDB                        |

| 13                                             | Field I/O 8                                   | 38                                         | DSR_A*                      | RXD_B                       | TXD+_B                      |

| 16                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 15                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 18                                             | Field I/O 9                                   | 5                                          | DCD_A*                      | RTS_B*                      | RXDB                        |

| 17                                             | Field I/O 10                                  | 39                                         | GND                         | CTS_B*                      | RXD+_B                      |

| 20                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 19                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 22                                             | Field I/O 11                                  | 6                                          | RI_B*                       | GND                         | GND                         |

| 21                                             | Field I/O 12                                  | 40                                         | DTR_B*                      | TXD_C                       | TXDC                        |

| 24                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 23                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 26                                             | Field I/O 13                                  | 7                                          | CTS_B*                      | RXD_C                       | TXD+_C                      |

| 25                                             | Field I/O 14                                  | 41                                         | TXD_B                       | RTS_C*                      | RXDC                        |

| 28                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 27                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 30                                             | Field I/O 15                                  | 8                                          | RTS_B*                      | CTS_C*                      | RXD+_C                      |

| 29                                             | Field I/O 16                                  | 42                                         | RXD_B                       | GND                         | GND                         |

| 32                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 31                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 34                                             | Field I/O 17                                  | 9                                          | DSR_B*                      | TXD_D                       | TXDD                        |

| 33                                             | Field I/O 18                                  | 43                                         | DCD_B*                      | RXD_D                       | TXD+_D                      |

#### Table 2.2 Field I/O 68 PinConnector Assignments

| Module/Carrier<br>Field I/O<br>Connector Pin # | Generic<br>Field I/O<br>Connector<br>Pin Name | Carrier 68-pin CHAMP I/O<br>Connector Pin# | AP500<br>Module<br>Function | AP520<br>Module<br>Function | AP521<br>Module<br>Function |

|------------------------------------------------|-----------------------------------------------|--------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| 36                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 35                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 38                                             | Field I/O 19                                  | 10                                         | GND                         | RTS_D*                      | RXDD                        |

| 37                                             | Field I/O 20                                  | 44                                         | GND                         | CTS_D*                      | RXD+_D                      |

| 40                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 39                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 42                                             | Field I/O 21                                  | 11                                         | GND                         | GND                         | GND                         |

| 41                                             | Field I/O 22                                  | 45                                         | GND                         | TXD_E                       | TXDE                        |

| 44                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 43                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 46                                             | Field I/O 23                                  | 12                                         | GND                         | RXD_E                       | TXD+_E                      |

| 45                                             | Field I/O 24                                  | 46                                         | GND                         | RTS_E*                      | RXDE                        |

| 48                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 47                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 50                                             | Field I/O 25                                  | 13                                         | GND                         | CTS_E*                      | RXD+_E                      |

| 49                                             | Field I/O 26                                  | 47                                         | GND                         | GND                         | GND                         |

| 52                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 51                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 54                                             | Field I/O 27                                  | 14                                         | RI_C*                       | TXD_F                       | TXDF                        |

| 53                                             | Field I/O 28                                  | 48                                         | DTR_C*                      | RXD_F                       | TXD+_F                      |

| 56                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 55                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 58                                             | Field I/O 29                                  | 15                                         | CTS_C*                      | RTS_F*                      | RXDF                        |

| 57                                             | Field I/O 30                                  | 49                                         | TXD_C                       | CTS_F*                      | RXD+_F                      |

| 60                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 59                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 62                                             | Field I/O 31                                  | 16                                         | RTS_C*                      | GND                         | GND                         |

| 61                                             | Field I/O 32                                  | 50                                         | RXD_C                       | TXD_G                       | TXDG                        |

| 64                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 63                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 66                                             | Field I/O 33                                  | 17                                         | DSR_C*                      | RXD_G                       | TXD+_G                      |

| 65                                             | Field I/O 34                                  | 51                                         | DCD_C*                      | RTS_G*                      | RXDG                        |

| 68                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 67                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 70                                             | Field I/O 35                                  | 18                                         | GND                         | CTS_G*                      | RXD+_G                      |

| Module/Carrier<br>Field I/O<br>Connector Pin # | Generic<br>Field I/O<br>Connector<br>Pin Name | Carrier 68-pin CHAMP I/O<br>Connector Pin# | AP500<br>Module<br>Function | AP520<br>Module<br>Function | AP521<br>Module<br>Function |

|------------------------------------------------|-----------------------------------------------|--------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| 69                                             | Field I/O 36                                  | 52                                         | RI_D*                       | GND                         | GND                         |

| 72                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 71                                             | RSVD/ISOL                                     |                                            |                             |                             |                             |

| 74                                             | Field I/O 37                                  | 19                                         | DTR_D*                      | TXD_H                       | TXDH                        |