Series IP560 Industrial I/O Pack CAN Bus Interface Module

# **USER'S MANUAL**

# ACROMAG INCORPORATED

30765 South Wixom Road P.O. BOX 437 Wixom, MI 48393-7037 U.S.A. Tel: (248) 295-0310 Fax: (248) 624-9234

Copyright 2010-2011, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice.

8500-887-C12A021

| 1 GENERAL INFORMATION                               |    |

|-----------------------------------------------------|----|

| 1.1 KEY IP560 FEATURES                              |    |

| 1.2 INDUSTRIAL I/O PACK INTERFACE FEATURES          |    |

| 1.3 INDUSTRIAL I/O PACK SOFTWARE LIBRARY            |    |

| 1.4 IP MODULE WINDOWS SOFTWARE                      |    |

| 1.4.1 IP MODULE VxWorks DRIVER SOFTWARE             |    |

| 1.4.2 IP MODULE Linux SOFTWARE                      |    |

| 2 PREPARATION FOR USE                               |    |

| 2.1 UNPACKING AND INSPECTION                        |    |

| 2.2 CARD CAGE CONSIDERATIONS                        |    |

| 2.3 BOARD CONFIGURATION                             |    |

| 2.3.1 Power Monitor Hardware Jumper Configuration   | 10 |

| 2.3.2 Default Hardware Jumper Configuration         | 11 |

| 2.3.3 Software Configuration                        | 11 |

| 2.4 CONNECTORS                                      | 11 |

| 2.4.1 IP Field I/O Connector (P2)                   | 11 |

| 2.4.2 IP Logic Interface Connector (P1)             | 12 |

| 3 PROGRAMMING INFORMATION                           | 13 |

| 3.1 IP IDENTIFICATION PROM                          | 13 |

| 3.2 I/O SPACE ADDRESS MAP                           | 14 |

| 3.2.1 Control Register 0                            | 15 |

| 3.2.2 Control Register 1                            |    |

| 3.2.3 Status Register                               | 17 |

| 3.2.4 Interrupt Vector Register 0                   | 17 |

| 3.2.5 Interrupt Vector Register 1                   | 17 |

| 3.3 MEMORY SPACE ADDRESS MAP                        | 18 |

| 3.4 Detailed description of the CAN controller      | 18 |

| 3.4.1 CAN 2.0B                                      |    |

| 3.4.2 DIFFERENCES BETWEEN BasicCAN AND PeliCAN MODE | 19 |

| 3.5 BasicCAN mode                                   | 19 |

| 3.5.1 Reset Values                                  | 23 |

| 3.5.2 Control Register (CR)                         | 26 |

| 3.5.3 Command Register (CMR)                        | 28 |

| 3.5.4 Status Register (SR)                          |    |

| 3.5.5 Interrupt Register (IR)                       |    |

| 3.5.6 Transmit Buffer Layout                        |    |

| 3.5.6.1 Identifier (ID).                            |    |

| 3.5.6.2 Remote Transmission Request (RTR)           |    |

| 3.5.6.3 Data Length Code (DLC)                      |    |

| 3.5.6.4 Data field                                  | 35 |

| 3.5.7 RECEIVE BUFFER                                | 35 |

| 3.5.8 ACCEPTANCE FILTER                             |    |

| 3.5.9 ACCEPTANCE MASK REGISTER (AMR)                |    |

| 3.5.10 Other registers                              |    |

| 3.6 PeliCAN mode                                    | 36 |

| 3.6.1 PeliCAN ADDRESS LAYOUT                        |    |

| 3.6.2 RESET VALUES                                  |    |

| 3.6.3 MODE REGISTER                                 |    |

| 3.6.4 Command Register (CMR)                        |    |

| 3.6.5 STATUS REGISTER (SR)                          | 51 |

| 3.6.6 INTERRUPT REGISTER (IR)                       |    |

| 3.6.7 INTERRUPT ENABLE REGISTER (IER)               | 55 |

| 3.6.8 ARBITRATION LOST CAPTURE (ALC)                | 56 |

| 3.6.9 ERROR CODE CAPTURE REGISTER (ECC)             |    |

| 3.6.10 ERROR WARNING LIMIT REGISTER (EWLR)          |    |

| 3.6.11 RX ERROR COUNTER REGISTER (RXERR)            |    |

| \ / / ·································             |    |

| 3.6.12<br>3.6.13 | TX ERROR COUNTER REGISTER (TXERR)                 |    |

|------------------|---------------------------------------------------|----|

|                  | TRANSMIT BUFFER                                   |    |

| 3.6.13.1         | Transmit buffer layout                            |    |

| 3.6.13.2         | Descriptor field of the transmit buffer           | 62 |

| 3.6.13.3         | Data Length Code (DLC)                            |    |

| 3.6.13.4         | Identifier (ID)                                   |    |

| 3.6.13.5         | Data field                                        |    |

| 3.6.14           | RECEIVE BUFFER                                    |    |

| 3.6.14.1         | Descriptor field of the receive buffer            |    |

| 3.6.15           | ACCEPTANCE FILTER                                 |    |

| 3.6.15.1         | Single filter configuration                       |    |

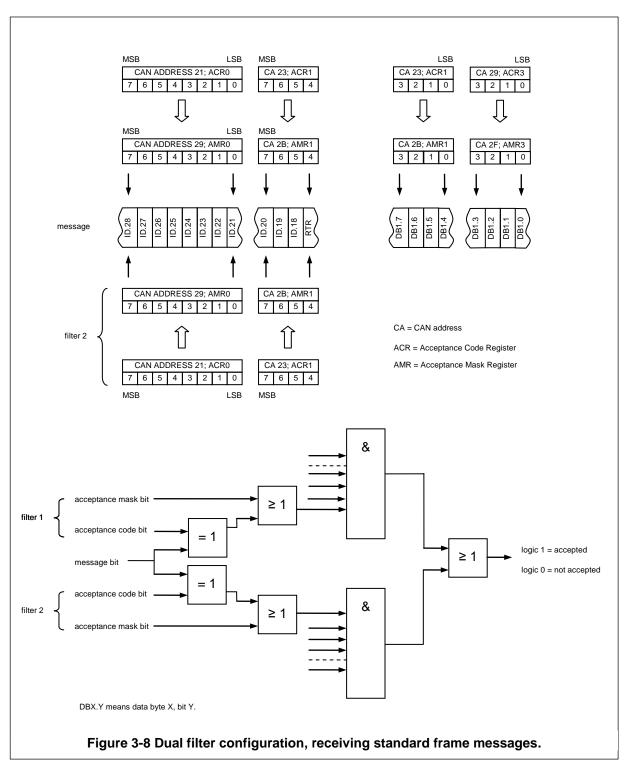

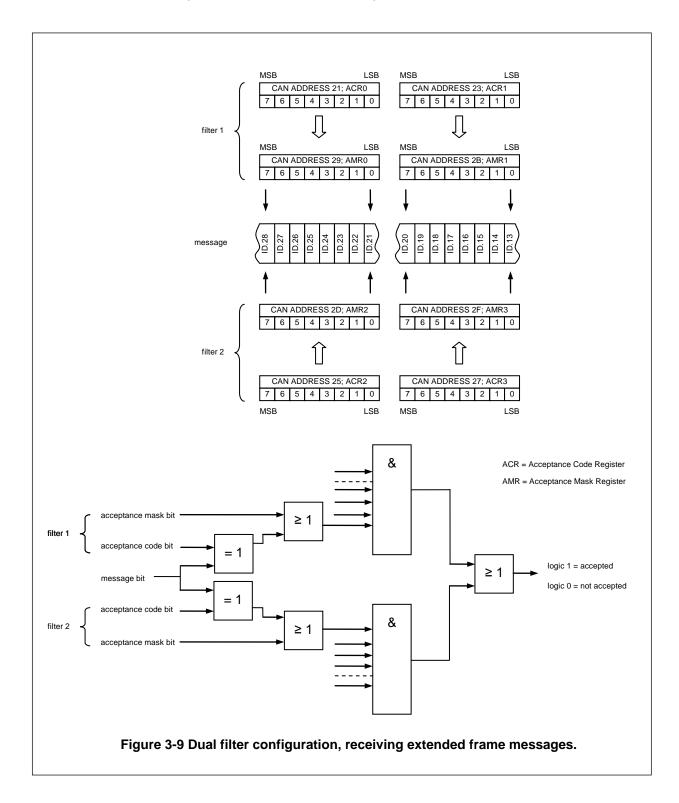

| 3.6.15.2         | Dual filter configuration                         | 69 |

| 3.6.16           | RX MESSAGE COUNTER (RMC)                          | 73 |

| 3.6.17           | RX BUFFER START ADDRESS REGISTER (RBSA)           |    |

| 3.7 Co           | ommon registers                                   | 74 |

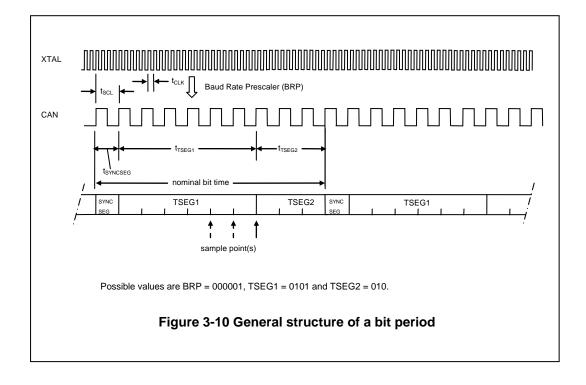

| 3.7.1            | BUS TIMING REGISTER 0 (BTR0)                      | 74 |

| 3.7.1.1          | Baud Rate Prescaler (BRP)                         | 74 |

| 3.7.1.2          | Synchronization Jump Width (SJW)                  | 74 |

| 3.7.1.3          | BUS TIMING REGISTER 1 (BTR1)                      | 74 |

| 3.7.1.4          | Time Segment 1 (TSEG1) and Time Segment 2 (TSEG2) |    |

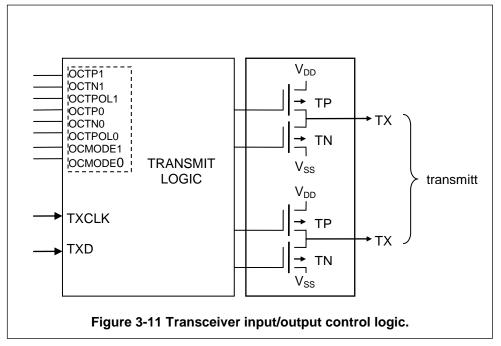

| 3.7.2            | OUTPUT CONTROL REGISTER (OCR)                     |    |

| 3.7.2.1          | Normal output mode                                |    |

| 3.7.2.2          | Clock output mode                                 |    |

| 3.7.2.3          | Bi-phase output mode                              |    |

| 3.7.2.4          | Test output mode                                  |    |

| 3.7.3            | CLOCK DIVIDER REGISTER (CDR)                      |    |

| 3.7.3.1          | CD.2 to CD.0                                      | 79 |

| 3.7.3.2          | Clock off                                         | 70 |

| 3.7.3.3          | RXINTEN                                           |    |

| 3.7.3.4          | CBP                                               |    |

|                  |                                                   |    |

| 3.7.3.5          |                                                   |    |

|                  |                                                   | 00 |

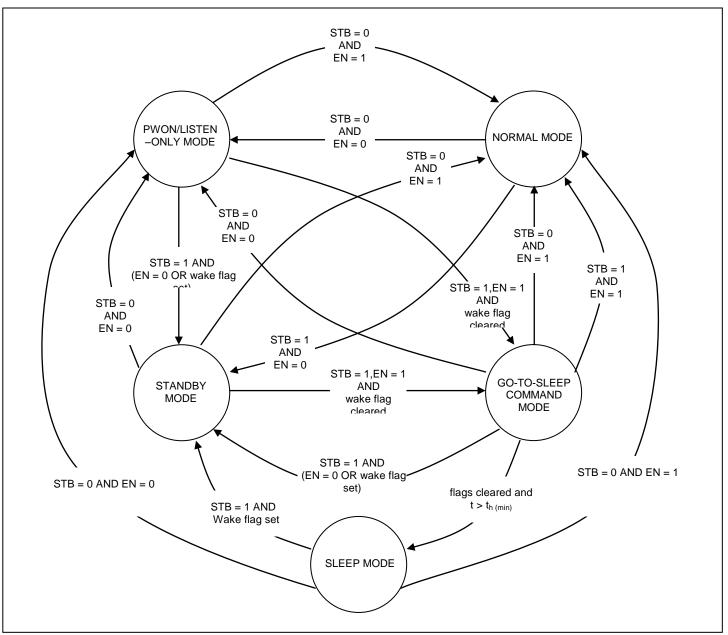

| 3.8.1            | TRANSCEIVER OPERATING MODES                       | 80 |

| 3.8.1.1          | NORMAL MODE                                       | 80 |

| 3.8.1.2          | Pwon/listen-only mode                             |    |

| 3.8.1.3          | Standby mode                                      |    |

| 3.8.1.4          | Go-to-sleep command mode                          |    |

| 3.8.1.5          | Sleep Mode                                        |    |

| 3.8.2            | Transceiver Internal Flags                        | 81 |

| 3.8.2.1          | UV <sub>NOM</sub> flag                            |    |

| 3.8.2.2          | UV <sub>BAT</sub> flag                            |    |

| 3.8.2.3          | Pwon flag                                         |    |

| 3.8.2.4          | Wake-Up flag                                      |    |

| 3.8.2.5          | Wake-up source flag                               |    |

| 3.8.2.6          | Bus failure flag                                  | 83 |

| 3.8.2.7          | Local failure flag                                | 83 |

| 3.8.3            | Local Failures                                    | 83 |

| 3.8.3.1          | TXD dominant clamping detection                   | 83 |

| 3.8.3.2          | RXD recessive clamping detection                  | 84 |

| 3.8.3.3          | TXD to RXD short circuit detection                |    |

| 3.8.3.4          | Bus dominant clamping detection                   |    |

| 3.8.3.5          | Overtemperature detection                         |    |

| 3.9 PI           | ROGRAMMING INTERRUPTS                             |    |

|                  | ORY OF OPERATION                                  |    |

|                  | OGIC/POWER INTERFACE                              |    |

|                  | INTERFACE LOGIC                                   |    |

|                  |                                                   |    |

| 4.3 | IP560 CONTROL LOGIC                 | . 87 |

|-----|-------------------------------------|------|

| 4.4 | ISOLATION (IP560(E)-I only)         | . 87 |

| 4.5 | CAN BUS TERMINATION                 | . 87 |

| 5   | SERVICE AND REPAIR                  | . 87 |

| 5.1 | SERVICE AND REPAIR ASSISTANCE       | . 87 |

| 5.2 | PRELIMINARY SERVICE PROCEDURE       | . 87 |

| 5.3 | WHERE TO GET HELP                   | . 88 |

| 6   | SPECIFICATIONS                      | . 89 |

| 6.1 | GENERAL SPECIFICATIONS              | . 89 |

| 6.2 | INDUSTRIAL I/O PACK COMPLIANCE      | . 89 |

| 7   | APPENDIX                            | . 93 |

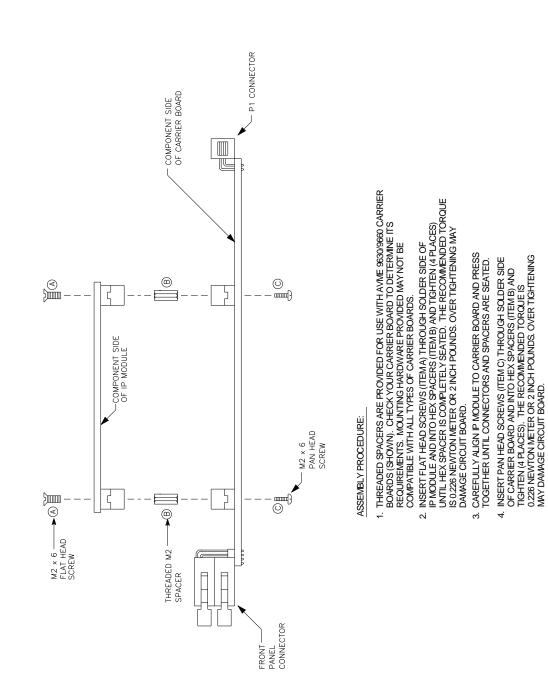

| 7.1 | IP MODULE TO CARRIER BOARD ASSEMBLY |      |

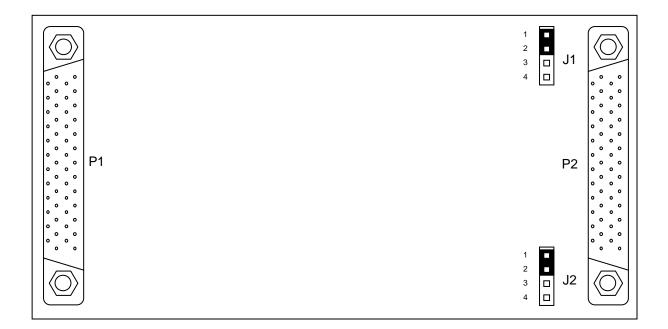

| 7.2 | JUMPER LOCATIONS                    | . 94 |

The information contained in this manual is subject to change without notice. Acromag, Inc. makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Further, Acromag, Inc. assumes no responsibility for any errors that may appear in this manual and makes no commitment to update, or keep current, the information contained in this manual. No part of this manual may be copied or reproduced in any form, without the prior written consent of Acromag, Inc.

#### IMPORTANT SAFETY CONSIDERATIONS

It is very important for the user to consider the possible adverse effects of power, wiring, component, sensor, or software failures in designing any type of control or monitoring system. This is especially important where economic property loss or human life is involved. It is important that the user employ satisfactory overall system design. It is agreed between the Buyer and Acromag, that this is the Buyer's responsibility.

#### 1 **GENERAL INFORMATION**

The Industrial I/O Pack (IP) Series IP560 module is a 16-bit, high density, single size IP, with the capability to interface to two Controller Area Network (CAN) 2.0B channels. The IP560 utilizes state of the art Surface Mounted Technology (SMT) to achieve its high channel density. Four units may be mounted on a 6U VME or CompactPCI carrier board to provide up to 8 CAN channels per bus system slot or 10 CAN channels per PCI bus (PC) system slot. The IP560 offers a variety of features which make it an ideal choice for many industrial and scientific applications as described below.

| Model    | Operating Temperature<br>Range |

|----------|--------------------------------|

| IP560    | 0 to 70°C                      |

| IP560E   | -40 to 85°C                    |

| IP560-I  | 0 to 70°C                      |

| IP560E-I | -40 to 85°C                    |

#### 1.1 **KEY IP560 FEATURES**

- **Two CAN channels**

- 1000 Volt isolation (IP560(E)-I) channel to channel and channel to host

- ISO 11898 compliance for standard (11-bit) and extended (29-bit) arbitration IDs

- CAN 2.0B protocol compatibility (extended frame passive in PCA82C200 compatibility mode) .

- NXP SJA1000 CAN controllers NXP TJA1043 high speed CAN transceivers

- Bit rates up to 1 Mbits/s .

- PCA82C200 mode (BasicCAN mode is default)

- Extended receive buffer (64-byte FIFO)

- Supports 11-bit identifier as well as 29-bit identifier

- 24 MHz clock frequency

#### **PeliCAN mode extensions:**

- Error counters with read/write access

- Programmable error warning limit

- Last error code register

- Error interrupt for each CAN-bus error

- Arbitration lost interrupt with detailed bit position

- Single-shot transmission (no re-transmission)

- Listen only mode (no acknowledge, no active error flags)

- Hot plugging support (software driven bit rate detection)

- Acceptance filter extension (4-byte code, 4-byte mask)

- Reception of 'own' messages (self reception request)

- Undervoltage detection on  $V_{BAT}$

- Listen-only mode for node diagnosis and failure containment

- ٠

- •

- TXD dominant clamping handler with diagnosis RXD recessive clamping handler with diagnosis TXD-to-RXD short-circuit handler with diagnosis Bus line short-circuit diagnosis Bus dominant clamping diagnosis ٠

- •

- •

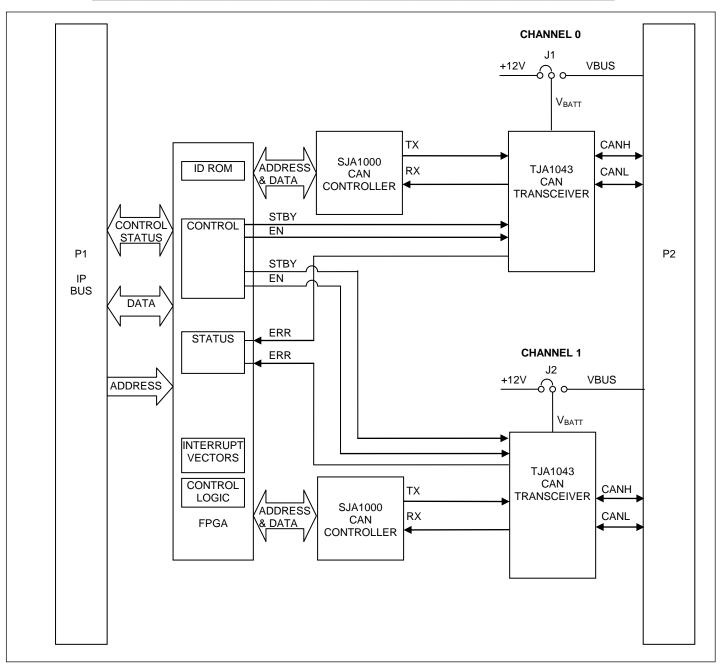

Figure 1-1 IP560(E) Block Diagram

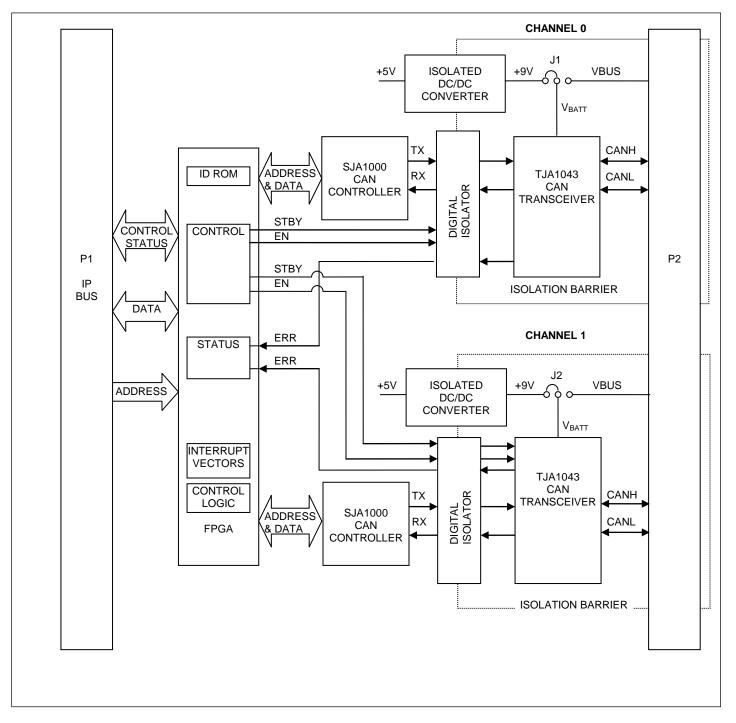

Figure 1-2 IP560(E)-I Block Diagram

### 1.2 INDUSTRIAL I/O PACK INTERFACE FEATURES

**High density -** Single-size, industry standard, IP module footprint. Four units mounted on a carrier board provide up to 8 channels in a single system slot. VMEbus and desktop PCI bus (PC) carriers are supported.

- Local ID Each IP module has its own 8-bit ID signature which can be read via access to the ID space.

- 8-bit I/O Control and status register Read/Write is performed through data transfer cycles in the IP module I/O space. Access to the SJA1000 CAN controllers is performed in memory space.

#### 1.3 INDUSTRIAL I/O PACK SOFTWARE LIBRARY

#### 1.4 IP MODULE WINDOWS SOFTWARE

Acromag provides a software product (sold separately) to facilitate the development of Windows (2000/XP/Vista/7®) applications accessing Acromag Industry Pack models installed on Acromag PCI Carrier Cards. This software (Model IPSW-API-WIN) consists of low-level drivers and Windows 32 Dynamic Link Libraries (DLLs) that are compatible with a number of programming environments including Visual C++™, Visual Basic .NET® and others. The DLL functions provide a high-level interface to boards eliminating the need to perform low-level reads/writes of registers, and the writing of interrupt handlers.

#### 1.4.1 IP MODULE VxWorks DRIVER SOFTWARE

Acromag provides a software product (sold separately) consisting of board VxWorks® software. This software (Model IPSW-API-VXW) is composed of VxWorks® (real time operating system) libraries for all Acromag IP modules and carriers including the AVME9670, AVME9600/9630, and APC8620A/21A. The software is implemented as a library of "C" functions which link with existing user code to make possible simple control of all Acromag PCI boards.

#### 1.4.2 IP MODULE Linux SOFTWARE

Acromag provides a software product (sold separately) consisting of board Linux® software. This software (Model IPSW-API-LNX) is composed of Linux® (real time operating system) libraries for all Acromag IP modules and carriers including the APC8620A/21A and APC8640. The software supports X86 PCI bus only and is implemented as library of "C" functions. These functions link with existing user code to make possible simple control of all Acromag IP modules and carriers.

### 2 PREPARATION FOR USE

#### 2.1 UNPACKING AND INSPECTION

Upon receipt of this product, inspect the shipping carton for evidence of mishandling during transit. If the shipping carton is badly damaged or water stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is absent when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, refer to the Acromag Service Policy to obtain return instructions. It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

This board is physically protected with packing material and electrically protected with an anti-static bag during shipment. However, it is recommended that the board be visually inspected for evidence of mishandling prior to applying power.

The board utilizes static sensitive components and should only be handled at a staticsafe workstation.

#### 2.2 CARD CAGE CONSIDERATIONS

Refer to the specifications for loading and power requirements. Be sure that the system power supplies are able to accommodate the power requirements of the carrier board, plus the installed IP modules, within the voltage tolerances specified.

IMPORTANT: Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature.

The dense packing of the IP modules to the carrier board restricts air flow within the card cage and is cause for concern. Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature and to prolong the life of the electronics. If the installation is in an industrial environment and the board is exposed to environmental air, careful consideration should be given to air-filtering.

#### 2.3 BOARD CONFIGURATION

The board may be configured differently, depending on the application. All possible jumper settings will be discussed in the following sections. The jumper locations are shown in the IP Mechanical Assembly Drawing located in the *Drawings* Section.

Remove power from the board when configuring hardware jumpers, installing IP modules, cables, termination panels, and field wiring. Refer to the IP560 Jumper Location drawing in section 7.1 and the following paragraphs for configuration and assembly instructions.

#### 2.3.1 Power Monitor Hardware Jumper Configuration

The IP560 series modules provide the capability to monitor the CAN bus supply voltage ( $V_{BAT}$ ) and report any under-voltage condition. This feature may be disabled by selecting an on-board power source to monitor. The selection of internal or external  $V_{BAT}$  power is accomplished via hardware jumpers J1 (channel 0) and J2 (channel 1) (see section 7.1). J1 and J2 select either the internal +12 Volt on-board supply or the external  $V_{BAT}$  supply sourced from the P2 connector. The configuration of the jumpers for the different supplies is shown in Table 2.1. "IN" means that the pins are shorted together with a shorting clip. "OUT" means that the clip has been removed. The jumper locations are shown in the IP560 Jumper Location drawing in section 7.1.

|                                 |               | Supply Selectio |

|---------------------------------|---------------|-----------------|

|                                 | Jn            | Jn              |

| Power Supply<br>Selection       | (Pins<br>1&2) | (Pins<br>3&4)   |

| +12 Volt on-board               | IN            | OUT             |

| V <sub>BAT</sub> (External, P2) | OUT           | IN              |

# Table 2.1 Power Supply Selections (Pins of J1 and J2)

#### 2.3.2 Default Hardware Jumper Configuration

When the board is shipped from the factory, it is configured as follows:

• Internal +12 Volt power supplies are used for V<sub>BAT</sub> monitoring

### 2.3.3 Software Configuration

Software configurable control registers are provided for control of transceiver mode and bus clock frequency. These control registers must be configured as desired before starting CAN communications. Refer to section 3 for programming details.

### 2.4 CONNECTORS

### 2.4.1 IP Field I/O Connector (P2)

P2 provides the field I/O interface connections for mating IP modules to the carrier board. P2 is a 50-pin female receptacle header which mates to the male connector of the carrier board. This provides excellent connection integrity and utilizes gold-plating in the mating area. Threaded metric M2 screws and spacers are supplied with the module to provide additional stability for harsh environments (see Mechanical Assembly Drawing 4501-434) near the end of this manual. The field and logic side connectors are keyed to avoid incorrect assembly.

P2 pin assignments are unique to each IP model (see Table 2.2) and normally correspond to the pin numbers of the field I/O interface connector on the carrier board (you should verify this for your carrier board).

| Pin         |        | Pin         |        |

|-------------|--------|-------------|--------|

| Description | Number | Description | Number |

| *N.C.       | 1      | N.C.        | 26     |

| VBAT_0      | 2      | VBAT_1      | 27     |

| N.C.        | 3      | N.C.        | 28     |

| N.C.        | 4      | N.C.        | 29     |

| GND_0       | 5      | GND_1       | 30     |

| CAN_H_0     | 6      | CAN_H_1     | 31     |

| CAN_L_0     | 7      | CAN_L_1     | 32     |

| GND_0       | 8      | GND_1       | 33     |

| N.C.        | 9      | N.C.        | 34     |

| N.C.        | 10     | N.C.        | 35     |

| N.C.        | 11     | N.C.        | 36     |

| N.C.        | 12     | N.C.        | 37     |

| N.C.        | 13     | N.C.        | 38     |

| N.C.        | 14     | N.C.        | 39     |

| N.C.        | 15     | N.C.        | 40     |

| N.C.        | 16     | N.C.        | 41     |

| N.C.        | 17     | N.C.        | 42     |

| N.C.        | 18     | N.C.        | 43     |

| N.C.        | 19     | N.C.        | 44     |

| N.C.        | 20     | N.C.        | 45     |

| N.C.        | 21     | N.C.        | 46     |

| N.C.        | 22     | N.C.        | 47     |

| N.C.        | 23     | N.C.        | 48     |

| N.C.        | 24     | N.C.        | 49     |

| N.C.        | 25     | N.C.        | 50     |

#### Table 2.2 IP560 Field I/O Pin Connections (P2)

\* Indicates pin not connected.

### 2.4.2 IP Logic Interface Connector (P1)

P1 of the IP module provides the logic interface to the mating connector on the carrier board. This connector is a 50-pin female receptacle header (AMP 173279-3 or equivalent) which mates to the male connector of the carrier board (AMP 173280-3 or equivalent). This provides excellent connection integrity and utilizes gold-plating in the mating area. Threaded metric M2 screws and spacers are supplied with the IP module to provide additional stability for harsh environments (see Drawing 4501-434 for assembly details). Field and logic side connectors are keyed to avoid incorrect assembly. The pin assignments of P1 are standard for all IP modules according to the Industrial I/O Pack Specification (see Table 2.3).

| Pin<br>Description | Number | Pin<br>Description | Number |  |

|--------------------|--------|--------------------|--------|--|

| GND                | 1      | GND                | 26     |  |

| CLK                | 2      | +5V                | 27     |  |

| Reset*             | 3      | R/W*               | 28     |  |

| D00                | 4      | IDSEL*             | 29     |  |

| D01                | 5      | DMAReq0*           | 30     |  |

| D02                | 6      | MEMSEL*            | 31     |  |

| D03                | 7      | DMAReq1*           | 32     |  |

| D04                | 8      | IntSel*            | 33     |  |

| D05                | 9      | DMAck0*            | 34     |  |

| D06                | 10     | IOSEL*             | 35     |  |

| D07                | 11     | RESERVED           | 36     |  |

| D08                | 12     | A1                 | 37     |  |

| D09                | 13     | DMAEnd*            | 38     |  |

| D10                | 14     | A2                 | 39     |  |

| D11                | 15     | ERROR*             | 40     |  |

| D12                | 16     | A3                 | 41     |  |

| D13                | 17     | INTReq0*           | 42     |  |

| D14                | 18     | A4                 | 43     |  |

| D15                | 19     | INTReq1*           | 44     |  |

| BS0*               | 20     | A5                 | 45     |  |

| BS1*               | 21     | STROBE*            | 46     |  |

| -12V               | 22     | A6                 | 47     |  |

| +12V               | 23     | ACK*               | 48     |  |

| +5V                | 24     | RESERVED           | 49     |  |

| GND                | 25     | GND                | 50     |  |

| Table 2.3 | Standard    | Logic Interface | Connections ( | (P1) |  |

|-----------|-------------|-----------------|---------------|------|--|

|           | o tan aan a | Logio internace |               | ,    |  |

An Asterisk (\*) is used to indicate an active-low signal. **BOLD ITALIC** Logic Lines are NOT USED by this IP Model.

### **3 PROGRAMMING INFORMATION**

#### 3.1 IP IDENTIFICATION PROM

Each IP module contains identification (ID) information that resides in the ID space per the IP module specification. This area of memory contains 32 bytes of information at most. Both fixed and variable information may be present within the ID space. Fixed information includes the "IPAH" identifier, model number, and manufacturer's identification codes. Variable information includes unique information required for the module. The IP560 ID information does not contain any variable (e.g. unique calibration) information. ID space bytes are addressed using only the odd addresses in a 64 byte block (on the "Big Endian" VMEbus). Even addresses are used on the "Little Endian" PC ISA bus. The IP560 ID space contents are shown in Table 3.1. Note that the base-address for the IP module ID space (see your carrier board instructions) must be added to the addresses shown to properly access the ID space. Execution of an ID space read requires 1 wait state.

| Hex<br>Offset<br>From ID<br>PROM<br>Base<br>Address | ASCII<br>Character<br>Equivalent | Numeric<br>Value<br>(Hex) | Field Description                                                 |

|-----------------------------------------------------|----------------------------------|---------------------------|-------------------------------------------------------------------|

| 01                                                  | I                                | 49                        | Format I ID ROM supports<br>8 or 32 MHz IP bus clock<br>frequency |

| 03                                                  | Р                                | 50                        |                                                                   |

| 05                                                  | Α                                | 41                        |                                                                   |

| 07                                                  | Н                                | 48                        |                                                                   |

| 09                                                  |                                  | A3                        | Acromag ID Code                                                   |

| 0B                                                  |                                  |                           | IP Model Code <sup>1</sup>                                        |

|                                                     |                                  | 50                        | IP560                                                             |

|                                                     |                                  | 51                        | IP560-I                                                           |

| 0D                                                  |                                  | 00                        | Not Used (Revision)                                               |

| 0F                                                  |                                  | 00                        | Reserved                                                          |

| 11                                                  |                                  | 00                        | Not Used (Driver ID Low Byte)                                     |

| 13                                                  |                                  | 00                        | Not Used (Driver ID High Byte)                                    |

| 15                                                  |                                  | 0C                        | Total Number of ID PROM Bytes                                     |

| 17                                                  |                                  |                           | CRC                                                               |

|                                                     |                                  | 6C                        | IP560                                                             |

|                                                     |                                  | 0D                        | IP560-I                                                           |

| 19 to 3F                                            |                                  | уу                        | Not Used                                                          |

#### Table 3.1 IP560 ID Space Identification (ID) PROM

#### Notes (Table 3.1):

1. The IP model number is represented by a two-digit code within the ID space (the IP560 model is represented by 50H, the IP560-I is represented by 51H).

#### 3.2 I/O SPACE ADDRESS MAP

This board is addressable in the Industrial Pack I/O space to provide access to control registers, a status register, and interrupt vector registers.

The I/O space may be as large as 64, 16-bit words (128 bytes) using address lines A1 to A6, but the IP560 uses only a portion of this space. The I/O space address map for the IP560 is shown in Table 3.2. Note that the base address for the IP module I/O space (see your carrier board instructions) must be added to the addresses shown to properly access the I/O space.

### Table 3.2 IP560 I/O Space Address (Hex) Memory Map<sup>1,2</sup>

| Base  | MSB           | MSB LSB |           | Base       |       |

|-------|---------------|---------|-----------|------------|-------|

| Addr+ | D15           | D08     | D07       | D00        | Addr+ |

| 00    | Not Used      |         | Control R | Register 0 | 01    |

| 02    | Not Used      |         | Control R | Register 1 | 03    |

| 04    | Not Used Stat |         | Status Re | egister    | 05    |

| 06    | Not Used      |         | Interrupt | Vector 0   | 07    |

| 08    | Not Used      |         | Interrupt | Vector 1   | 09    |

#### Notes (Table 3.2):

- 1. All addresses that are "Not Used" will read as zero.

- 2. All Reads are one wait state. All writes are zero wait state.

#### 3.2.1 Control Register 0

This read/write register is used to select the transceiver mode and enable/disable interrupts for each CAN channel.

The function of each of the control register bits is described in Table 3.3. A power-up or system reset sets all control register bits to 0.

| BIT | FUNCTION                          |

|-----|-----------------------------------|

| 0   | Not Used <sup>1</sup>             |

| 1   | STB Channel 0 <sup>2</sup>        |

|     | CAN transceiver standby Channel 0 |

|     | 0 = Standby                       |

|     | 1 = Active                        |

| 2   | EN Channel 0 <sup>2</sup>         |

|     | CAN transceiver enable Channel 0  |

|     | 0 = Disabled                      |

|     | 1 = Enabled                       |

| 3   | Channel 0 interrupt enable        |

|     | 0 = Disabled                      |

|     | 1 = Enabled                       |

| 4   | Not Used <sup>1</sup>             |

| 5   | STB Channel 1 <sup>2</sup>        |

|     | CAN transceiver standby Channel 1 |

|     | 0 = Standby                       |

|     | 1 = Active                        |

| 6   | EN Channel 1 <sup>2</sup>         |

|     | CAN transceiver enable Channel 1  |

|     | 0 = Disabled                      |

|     | 1 = Enabled                       |

| 7   | Channel 1 interrupt enable        |

|     | 0 = Disabled                      |

|     | 1 = Enabled                       |

### Table 3.3 Control Register 0

#### Notes (Table 3.3):

- 1. All bits labeled "Not Used" will return the last value written on a read access.

- 2. See section 3.7 for further description.

#### 3.2.2 Control Register 1

This read/write register is used to select the IP bus clock frequency and enable the clock for the CAN controllers.

The function of each of the control register bits is described in Table 3.4. A power-up or system reset sets all control register bits to 0.

| BIT   | FUNCTION              |

|-------|-----------------------|

| 0     | IP bus clock 0        |

| 1     | IP bus clock 1        |

| 2 - 7 | Not Used <sup>1</sup> |

#### Table 3.4 Control Register 1

#### Notes (Table 3.4):

1. All bits labeled "Not Used" will return the last value written on a read access.

IP bus clock: A phase locked loop is used to generate the module clock from the IP bus clock. The IP bus clock must remain constant after setting the appropriate bits in this register. Set the IP bus clock frequency on the carrier board prior to writing these bits. The module clock is not enabled until the IP bus clock frequency is specified by writing the following bit pattern:

Table 3.5 IP bus clock selection

| IP bus clock 1 | k 1 IP bus clock 0 FUNCTION |                                          |

|----------------|-----------------------------|------------------------------------------|

| 0              | 0                           | Module clock disabled                    |

| 0              | 1                           | IP bus clock 8 MHz, enable module clock  |

| 1              | X <sup>1</sup>              | IP bus clock 32 MHz, enable module clock |

#### Notes (Table 3.5):

1. All bits labeled "X" can be 0 or 1.

If the IP bus clock frequency on the carrier board must be changed after setting the IP bus clock selection bits in the IP560 Control Register 1, then the IP560 must be reset and the IP bus clock selection bits must be set for the new IP bus clock frequency.

#### 3.2.3 Status Register

This read only register is used to indicate interrupt and transceiver status for each of the CAN channels.

The function of each of the status register bits is described in Table 3.6. A power-up or system reset sets all control register bits to 0.

| BIT   | FUNCTION                                                                   |

|-------|----------------------------------------------------------------------------|

| 0     | Interrupt Pending Channel 0                                                |

|       | 0 = No interrupt pending                                                   |

|       | 1 = Interrupt Pending                                                      |

| 1     | Transceiver Error Channel 0                                                |

|       | The error output pin from the TJA1043 CAN transceiver is connected to this |

|       | status bit                                                                 |

|       | 0 = No error                                                               |

|       | 1 = Error                                                                  |

| 2     | Interrupt Pending Channel 1                                                |

|       | 0 = No interrupt pending                                                   |

|       | 1 = Interrupt Pending                                                      |

| 3     | Transceiver Error Channel 1                                                |

|       | The error output pin from the TJA1043 CAN transceiver is connected to this |

|       | status bit                                                                 |

|       | 0 = No error                                                               |

|       | 1 = Error                                                                  |

| 4     | Module clock ready <sup>2</sup>                                            |

|       | 0 = not ready                                                              |

|       | 1 = ready                                                                  |

| 5 - 7 | Not Used <sup>1</sup>                                                      |

| Table 3.6 Status | Register |

|------------------|----------|

|------------------|----------|

#### Notes (Table 3.6):

- 1. All bits labeled "Not Used" will return zero on a read access.

- 2. Module clock ready may take up to 5 mS to indicate ready after setting the appropriate clock enable bit.

#### 3.2.4 Interrupt Vector Register 0

The Interrupt Vector Register 0 can be written with an 8-bit interrupt vector. This vector is provided to the carrier and system bus upon an active INTSEL\* cycle. The register contents are cleared upon reset.

| Interrupt Vector Register 0 |    |    |    |    |    |     |    |

|-----------------------------|----|----|----|----|----|-----|----|

| MSB LSB                     |    |    |    |    |    | LSB |    |

| 07                          | 06 | 05 | 04 | 03 | 02 | 01  | 00 |

Interrupt 0 is released by clearing the interrupt condition of the Channel 0 SJA1000 CAN controller.

#### 3.2.5 Interrupt Vector Register 1

The Interrupt Vector Register 1 can be written with an 8-bit interrupt vector. This vector is provided to the carrier and system bus upon an active INTSEL\* cycle. The register contents are cleared upon reset.

| Interrupt Vector Register 1 |    |    |    |    |    |    |     |

|-----------------------------|----|----|----|----|----|----|-----|

| MSB                         |    |    |    |    |    |    | LSB |

| 07                          | 06 | 05 | 04 | 03 | 02 | 01 | 00  |

Interrupt 1 is released by clearing the interrupt condition of the Channel 1 SJA1000 CAN controller.

#### 3.3 MEMORY SPACE ADDRESS MAP

This board is addressable in the Industrial Pack memory space to access the SJA1000 CAN controllers. The IP560 uses the lower 512 words of this memory space. The SJA1000 controller has two modes of operation: BasicCAN and PeliCAN. The memory maps differ depending on the mode selected. The memory space address map for the IP560 in BasicCAN mode is shown in Table 3.7, PeliCAN mode is shown in Table 3.16. Note that the base address for the IP module memory space (see your carrier board instructions) must be added to the addresses shown to properly access the memory space. 8-bit and 16-bit accesses to the registers in memory space are permitted, but the upper 8 bits of the 16-bit access are ignored on writes and read as zeros.

This memory map reflects byte accesses using the "Big Endian" byte ordering format. Big Endian is the convention used in the Motorola 68000 microprocessor family and is the VMEbus convention. In Big Endian, the lower-order byte is stored at odd-byte addresses. The Intel x86 family of microprocessors uses the opposite convention, or "Little Endian" byte ordering. Little Endian uses even-byte addresses to store the low-order byte. As such, installation of this module on a PC carrier board will require the use of the even address locations to access the lower 8-bits of data while on a VMEbus carrier use of odd address locations are required to access the lower 8-bit data.

#### 3.4 Detailed description of the CAN controller

The SJA1000 supports two different modes of operation:

- BasicCAN mode

- PeliCAN mode; with extended features.

The mode of operation is selected with the CAN-mode bit located within the clock divider register (see section 3.7.3). The default mode upon reset is the BasicCAN mode.

#### 3.4.1 CAN 2.0B

The SJA1000 is designed to support the full CAN 2.0B protocol specification, which means that the extended oscillator tolerance is implemented as well as the processing of extended frame messages. In BasicCAN mode it is possible to transmit and receive standard frame messages only (11-bit identifier). If extended frame messages (29-bit identifier) are detected on the CAN-bus, they are tolerated and an acknowledge is given if the message was correct, but there is no receive interrupt generated (i.e. the message is discarded).

#### 3.4.2 DIFFERENCES BETWEEN BasicCAN AND PeliCAN MODE

In the PeliCAN mode the SJA1000 appears with a reorganized register mapping and additional features. In the PeliCAN mode the complete CAN 2.0B functionality is supported (29-bit identifier).

PeliCAN mode provides the following additional features:

- Reception and transmission of standard and extended frame format messages

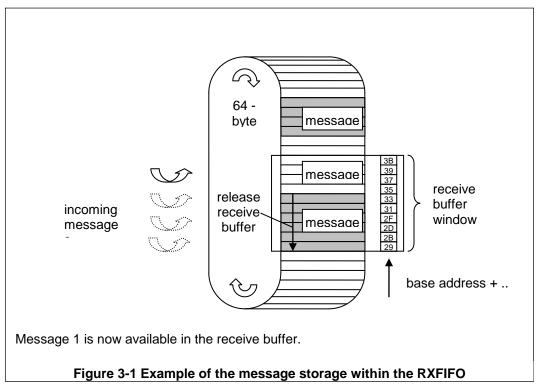

- Receive FIFO (64-byte)

- Single/dual acceptance filter with mask and code register for standard and extended frame

- Error counters with read/write access

- Programmable error warning limit

- Last error code register

- Error interrupt for each CAN-bus error

- Arbitration lost interrupt with detailed bit position

- Single-shot transmission (no re-transmission on error or arbitration lost)

- Listen only mode (monitoring of the CAN-bus, no acknowledge, no error flags)

- Hot plugging supported (disturbance-free software driven bit rate detection)

- Disable CLKOUT by hardware.

#### 3.5 BasicCAN mode

The address area of the SJA1000 consists of the control segment and the message buffers. The control segment is programmed during an initialization download in order to configure communication parameters (e.g. bit timing). Communication over the CAN-bus is also controlled via this segment by the processor.

A message, which should be transmitted, has to be written to the transmit buffer. After a successful reception the host processor may read the received message from the receive buffer and then release it for further use.

The exchange of status, control and command signals between the processor and the SJA1000 is performed in the control segment. The layout of this segment is shown in Table 3.7. After the initial download, the contents of the register's acceptance code, acceptance mask, bus timing registers 0 and 1 and output control should not be changed. Therefore these registers may only be accessed when the reset request bit in the control register is set HIGH.

For register access, two different modes have to be distinguished:

- Reset mode

- Operating mode.

The reset mode (see Table 3.9, control register, bit Reset Request) is entered automatically after a hardware reset or when the controller enters the bus-off state (see Table 3.11, status register, bit Bus Status). The operating mode is activated by setting the reset request bit in the control register to zero.

| Table 3.7 IP560 Memory Space Address  | (Hex) Memory Ma | n BasicCAN see note 1 |

|---------------------------------------|-----------------|-----------------------|

| Table 3.7 IF 500 Memory Space Address | (nex) wemory wa | Dasicuan see note i   |

| Hex<br>Offset<br>From<br>Base<br>Addr | MSB<br>D15 D08       | LSB<br>D07 D00                         |                                        |                                              |                                              |          |  |  |

|---------------------------------------|----------------------|----------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------------|----------|--|--|

|                                       |                      | OPERAT                                 | ING MODE                               | RESE                                         | MODE                                         |          |  |  |

|                                       |                      | READ                                   | WRITE                                  | READ                                         | WRITE                                        |          |  |  |

|                                       | 8                    |                                        | CHANNEL 0                              |                                              |                                              |          |  |  |

| 00                                    | Not Used             | control                                | control                                | control                                      | control                                      | 01       |  |  |

| 02                                    | Not Used             | (FFH)                                  | command                                | (FFH)                                        | command                                      | 03       |  |  |

| 04                                    | Not Used             | statuś                                 | -                                      | status                                       | -                                            | 05       |  |  |

| 06                                    | Not Used             | interrupt                              | -                                      | interrupt                                    | -                                            | 07       |  |  |

| 08                                    | Not Used             | (FFH)                                  | -                                      | acceptance                                   | acceptance                                   | 09       |  |  |

| 0A                                    | Not Used             | (FFH)                                  | -                                      | code<br>acceptance                           | code<br>acceptance                           | 0B       |  |  |

| 0C                                    | Not Used             | (FFH)                                  | -                                      | mask<br>bus timing 0                         | mask<br>bus timing 0                         | 0D       |  |  |

| 0C<br>0E                              | Not Used             | (FFH)                                  | -                                      | bus timing 1                                 | bus timing 0                                 | 0D<br>0F |  |  |

| 10                                    | Not Used             | (FFH)                                  |                                        |                                              | output                                       | 11       |  |  |

|                                       |                      |                                        |                                        | control                                      | control                                      |          |  |  |

| 12                                    | Not Used             | test <sup>2</sup>                      | test <sup>2</sup>                      | test <sup>2</sup>                            | test <sup>2</sup>                            | 13       |  |  |

| 14                                    | Not Used             | TX identifier (10 to 3)                | TX identifier (10 to 3)                | (FFH)                                        | -                                            | 15       |  |  |

| 16                                    | Not Used             | TX identifier (2 to 0),<br>RTR and DLC | TX identifier (2 to 0),<br>RTR and DLC | (FFH)                                        | -                                            | 17       |  |  |

| 18                                    | Not Used             | TX buffer data byte 1                  | TX buffer data byte 1                  | (FFH)                                        | -                                            | 19       |  |  |

| 1A                                    | Not Used             | TX buffer data byte 2                  | TX buffer data byte 2                  | (FFH)                                        | -                                            | 1B       |  |  |

| 1C                                    | Not Used             | TX buffer data byte 3                  | TX buffer data byte 3                  | (FFH)                                        | -                                            | 1D       |  |  |

| 1E                                    | Not Used             | TX buffer data byte 4                  | TX buffer data byte 4                  | (FFH)                                        | -                                            | 1F       |  |  |

| 20                                    | Not Used             | TX buffer data byte 5                  | TX buffer data byte 5                  | (FFH)                                        | -                                            | 21       |  |  |

| 22                                    | Not Used             | TX buffer data byte 6                  | TX buffer data byte 6                  | (FFH)                                        | -                                            | 23       |  |  |

| 24                                    | Not Used             | TX buffer data byte 7                  | TX buffer data byte 7                  | (FFH)                                        | -                                            | 25<br>27 |  |  |

| 26<br>28                              | Not Used<br>Not Used | TX buffer data byte 8                  | TX buffer data byte 8                  | (FFH)                                        | -                                            | 27<br>29 |  |  |

|                                       |                      | RX identifier (10 to 3)                | RX identifier (10 to 3)                | RX identifier<br>(10 to 3)                   | RX identifier<br>(10 to 3)                   |          |  |  |

| 2A                                    | Not Used             | RX identifier (2 to 0),<br>RTR and DLC | RX identifier (2 to 0),<br>RTR and DLC | RX identifier<br>(2 to 0),<br>RTR and<br>DLC | RX identifier<br>(2 to 0),<br>RTR and<br>DLC | 2B       |  |  |

| 2C                                    | Not Used             | RX buffer data byte 1                  | RX buffer data byte 1                  | RX buffer<br>data byte 1                     | RX buffer<br>data byte 1                     | 2D       |  |  |

| 2E                                    | Not Used             | RX buffer data byte 2                  | RX buffer data byte 2                  | RX buffer<br>data byte 2                     | RX buffer<br>data byte 2                     | 2F       |  |  |

| 30                                    | Not Used             | RX buffer data byte 3                  | RX buffer data byte 3                  | RX buffer<br>data byte 3                     | RX buffer<br>data byte 3                     | 31       |  |  |

| 32                                    | Not Used             | RX buffer data byte 4                  | RX buffer data byte 4                  | RX buffer<br>data byte 4                     | RX buffer<br>data byte 4                     | 33       |  |  |

| 34                                    | Not Used             | RX buffer data byte 5                  | RX buffer data byte 5                  | RX buffer<br>data byte 5                     | RX buffer<br>data byte 5                     | 35       |  |  |

| 36                                    | Not Used             | RX buffer data byte 6                  | RX buffer data byte 6                  | RX buffer<br>data byte 6                     | RX buffer<br>data byte 6                     | 37       |  |  |

| 38                                    | Not Used             | RX buffer data byte 7                  | RX buffer data byte 7                  | RX buffer<br>data byte 7                     | RX buffer<br>data byte 7                     | 39       |  |  |

| 3A                                    | Not Used             | RX buffer data byte 8                  | RX buffer data byte 8                  | RX buffer<br>data byte 8                     | RX buffer<br>data byte 8                     | 3B       |  |  |

| 3C                                    | Not Used             | (FFH)                                  | -                                      | (FFH)                                        | -                                            | 3D       |  |  |

| 3E                                    | Not Used             | Clock divider <sup>3</sup>             | Clock divider <sup>3</sup>             | Clock                                        | Clock                                        | 3F       |  |  |

|                                       |                      | l                                      |                                        | divider <sup>3</sup>                         | divider <sup>3</sup>                         |          |  |  |

| Hex<br>Offset<br>From<br>Base<br>Addr | MSB<br>D15 D08       |                                                | LSB<br>D07 D00                                 |                                              |                                              | Hex<br>Offset<br>From<br>Base<br>Addr |

|---------------------------------------|----------------------|------------------------------------------------|------------------------------------------------|----------------------------------------------|----------------------------------------------|---------------------------------------|

|                                       |                      |                                                | ING MODE                                       |                                              | MODE                                         |                                       |

|                                       |                      | READ                                           | WRITE                                          | READ                                         | WRITE                                        |                                       |

| 000                                   |                      |                                                | Channel 1                                      |                                              |                                              | 004                                   |

| 200                                   | Not Used             | control                                        | control                                        | control                                      | control                                      | 201                                   |

| 202<br>204                            | Not Used<br>Not Used | (FFH)                                          | command                                        | (FFH)                                        | command                                      | 203<br>205                            |

| 204                                   | Not Used             | status<br>interrupt                            | -                                              | status                                       | -                                            | 203                                   |

| 208                                   | Not Used             | (FFH)                                          | -                                              | interrupt<br>acceptance                      | -<br>acceptance                              | 209                                   |

|                                       | Not Oscu             | (111)                                          | -                                              | code                                         | code                                         |                                       |

| 20A                                   | Not Used             | (FFH)                                          | -                                              | acceptance<br>mask                           | acceptance<br>mask                           | 20B                                   |

| 20C                                   | Not Used             | (FFH)                                          | -                                              | bus timing 0                                 | bus timing 0                                 | 20D                                   |

| 20E                                   | Not Used             | (FFH)                                          | -                                              | bus timing 1                                 | bus timing 1                                 | 20F                                   |

| 210                                   | Not Used             | (FFH)                                          | -                                              | output<br>control                            | output<br>control                            | 211                                   |

| 212                                   | Not Used             | test <sup>2</sup>                              | test <sup>2</sup>                              | test <sup>2</sup>                            | test <sup>2</sup>                            | 213                                   |

| 214                                   | Not Used             | TX identifier (10 to 3)                        | TX identifier (10 to 3)                        | (FFH)                                        | -                                            | 215                                   |

| 216                                   | Not Used             | TX identifier (2 to 0),<br>RTR and DLC         | TX identifier (2 to 0),<br>RTR and DLC         | (FFH)                                        | -                                            | 217                                   |

| 218                                   | Not Used             | TX buffer data byte 1                          | TX buffer data byte 1                          | (FFH)                                        | -                                            | 219                                   |

| 21A                                   | Not Used             | TX buffer data byte 2                          | TX buffer data byte 2                          | (FFH)                                        | -                                            | 21B                                   |

| 21C                                   | Not Used             | TX buffer data byte 3                          | TX buffer data byte 3                          | (FFH)                                        | -                                            | 21D                                   |

| 21E                                   | Not Used             | TX buffer data byte 4                          | TX buffer data byte 4                          | (FFH)                                        | -                                            | 21F                                   |

| 220                                   | Not Used             | TX buffer data byte 5                          | TX buffer data byte 5                          | (FFH)                                        | -                                            | 221<br>223                            |

| 222<br>224                            | Not Used<br>Not Used | TX buffer data byte 6                          | TX buffer data byte 6                          | (FFH)                                        | -                                            | 225                                   |

| 224                                   | Not Used             | TX buffer data byte 7<br>TX buffer data byte 8 | TX buffer data byte 7<br>TX buffer data byte 8 | (FFH)<br>(FFH)                               | -                                            | 225                                   |

| 220                                   | Not Used             | RX identifier (10 to 3)                        | RX identifier (10 to 3)                        | RX identifier                                | -<br>RX identifier                           | 229                                   |

|                                       |                      | · · · · · ·                                    | . , ,                                          | (10 to 3)                                    | (10 to 3)                                    |                                       |

| 22A                                   | Not Used             | RX identifier (2 to 0),<br>RTR and DLC         | RX identifier (2 to 0),<br>RTR and DLC         | RX identifier<br>(2 to 0),<br>RTR and<br>DLC | RX identifier<br>(2 to 0),<br>RTR and<br>DLC | 22B                                   |

| 22C                                   | Not Used             | RX buffer data byte 1                          | RX buffer data byte 1                          | RX buffer<br>data byte 1                     | RX buffer<br>data byte 1                     | 22D                                   |

| 22E                                   | Not Used             | RX buffer data byte 2                          | RX buffer data byte 2                          | RX buffer<br>data byte 2                     | RX buffer<br>data byte 2                     | 22F                                   |

| 230                                   | Not Used             | RX buffer data byte 3                          | RX buffer data byte 3                          | RX buffer<br>data byte 3                     | RX buffer<br>data byte 3                     | 231                                   |

| 232                                   | Not Used             | RX buffer data byte 4                          | RX buffer data byte 4                          | RX buffer<br>data byte 4                     | RX buffer<br>data byte 4                     | 233                                   |

| 234                                   | Not Used             | RX buffer data byte 5                          | RX buffer data byte 5                          | RX buffer<br>data byte 5                     | RX buffer<br>data byte 5                     | 235                                   |

| 236                                   | Not Used             | RX buffer data byte 6                          | RX buffer data byte 6                          | RX buffer<br>data byte 6                     | RX buffer<br>data byte 6                     | 237                                   |

| 238                                   | Not Used             | RX buffer data byte 7                          | RX buffer data byte 7                          | RX buffer<br>data byte 7                     | RX buffer<br>data byte 7                     | 239                                   |

| 23A                                   | Not Used             | RX buffer data byte 8                          | RX buffer data byte 8                          | RX buffer<br>data byte 8                     | RX buffer<br>data byte 8                     | 23B                                   |

| 23C                                   | Not Used             | (FFH)                                          | -                                              | (FFH)                                        | -                                            | 23D                                   |

| 23E                                   | Not Used             | Clock divider <sup>3</sup>                     | Clock divider <sup>3</sup>                     | Člock<br>divider <sup>3</sup>                | Clock<br>divider <sup>3</sup>                | 23F                                   |

Notes:(Table 3.7):

1. Registers are repeated within higher CAN address areas (the most significant bits of the lower 8-bit portion of the address are not decoded: address 4016 maps to address 0 and address 14016 maps to 10016)

- 2. Test register is used for production testing only. Using this register during normal operation may result in undesired device behavior.

- 3. Some bits are writeable in reset mode only (CAN mode, CBP, and clock off)

#### 3.5.1 Reset Values

Detection of a 'reset request' results in aborting the current transmission/reception of a message and entering the reset mode. On the '1-to-0' transition of the reset request bit, the CAN controller returns to the operating mode.

|          |       |        |                                 | VA                   | LUE                                                        |

|----------|-------|--------|---------------------------------|----------------------|------------------------------------------------------------|

| REGISTER | BIT   | SYMBOL | NAME                            | RESET BY<br>HARDWARE | SETTING<br>BIT CR.0 BY<br>SOFTWARE<br>OR DUE TO<br>BUS-OFF |

| Control  | CR.7  | -      | reserved                        | 0                    | 0                                                          |

|          | CR.6  | -      | reserved                        | Х                    | Х                                                          |

|          | CR.5  | -      | reserved                        | 1                    | 1                                                          |

|          | CR.4  | OIE    | Overrun Interrupt<br>Enable     | Х                    | Х                                                          |

|          | CR.3  | EIE    | Error Interrupt<br>Enable       | Х                    | Х                                                          |

|          | CR.2  | TIE    | Transmit<br>Interrupt Enable    | X                    | Х                                                          |

|          | CR.1  | RIE    | Receive Interrupt<br>Enable     | X                    | Х                                                          |

|          | CR.0  | RR     | Reset Request                   | 1 (reset<br>mode)    | 1 (reset<br>mode)                                          |

| Command  | CMR.7 | -      | reserved                        | note 3               | note 3                                                     |

|          | CMR.6 | -      | reserved                        |                      |                                                            |

|          | CMR.5 | -      | reserved                        |                      |                                                            |

|          | CMR.4 | GTS    | Go To Sleep                     |                      |                                                            |

|          | CMR.3 | CDO    | Clear Data<br>Overrun           |                      |                                                            |

|          | CMR.2 | RRB    | Release Receive<br>Buffer       |                      |                                                            |

|          | CMR.1 | AT     | Abort<br>Transmission           |                      |                                                            |

|          | CMR.0 | TR     | Transmission<br>Request         |                      |                                                            |

| Status   | SR.7  | BS     | Bus Status                      | 0 (bus-on)           | Х                                                          |

|          | SR.6  | ES     | Error Status                    | 0 (ok)               | Х                                                          |

|          | SR.5  | TS     | Transmit Status                 | 0 (idle)             | 0 (idle)                                                   |

|          | SR.4  | RS     | Receive Status                  | 0 (idle)             | 0 (idle)                                                   |

|          | SR.3  | TCS    | Transmission<br>Complete Status | 1 (complete)         | Х                                                          |

|          | SR.2  | TBS    | Transmit Buffer<br>Status       | 1 (released)         | 1 (released)                                               |

Table 3.8 Reset mode configuration; notes 1 and 2

|                    |                      |     |                           | VA                   | LUE                                                        |

|--------------------|----------------------|-----|---------------------------|----------------------|------------------------------------------------------------|

| REGISTER           | STER BIT SYMBOL NAME |     | NAME                      | RESET BY<br>HARDWARE | SETTING<br>BIT CR.0 BY<br>SOFTWARE<br>OR DUE TO<br>BUS-OFF |

|                    | SR.1                 | DOS | Data Overrun<br>Status    | 0 (absent)           | 0 (absent)                                                 |

|                    | SR.0                 | RBS | Receive Buffer<br>Status  | 0 (empty)            | 0 (empty)                                                  |

| Interrupt          | IR.7                 | -   | reserved                  | 1                    | 1                                                          |

|                    | IR.6                 | -   | reserved                  | 1                    | 1                                                          |

|                    | IR.5                 | -   | reserved                  | 1                    | 1                                                          |

|                    | IR.4                 | WUI | Wake-Up<br>Interrupt      | 0 (reset)            | 0 (reset)                                                  |

|                    | IR.3                 | DOI | Data Overrun<br>Interrupt | 0 (reset)            | 0 (reset)                                                  |

|                    | IR.2                 | EI  | Error Interrupt           | 0 (reset)            | X; note 4                                                  |

|                    | IR.1                 | TI  | Transmit<br>Interrupt     | 0 (reset)            | O (reset)                                                  |

|                    | IR.0                 | RI  | Receive Interrupt         | 0 (reset)            | O (reset)                                                  |

| Acceptance code    | AC.7 to<br>0         | AC  | Acceptance<br>Code        | X                    | X                                                          |

| Acceptance<br>mask | AM.7 to<br>0         | AM  | Acceptance<br>Mask        | Х                    | Х                                                          |

|              |                    |         |                                 | VA                   | LUE                                                        |

|--------------|--------------------|---------|---------------------------------|----------------------|------------------------------------------------------------|

| REGISTER     | ER BIT SYMBOL NAME |         | NAME                            | RESET BY<br>HARDWARE | SETTING<br>BIT CR.0 BY<br>SOFTWARE<br>OR DUE TO<br>BUS-OFF |

| Bus timing 0 | BTR0.7             | SJW.1   | Synchronization<br>Jump Width 1 | X                    | Х                                                          |

|              | BTR0.6             | SJW.0   | Synchronization<br>Jump Width 0 | X                    | Х                                                          |

|              | BTR0.5             | BRP.5   | Baud Rate<br>Prescaler 5        | X                    | Х                                                          |

|              | BTR0.4             | BRP.4   | Baud Rate<br>Prescaler 4        | X                    | Х                                                          |

|              | BTR0.3             | BRP.3   | Baud Rate<br>Prescaler 3        | X                    | Х                                                          |

|              | BTR0.2             | BRP.2   | Baud Rate<br>Prescaler 2        | X                    | Х                                                          |

|              | BTR0.1             | BRP.1   | Baud Rate<br>Prescaler 1        | X                    | Х                                                          |

|              | BTR0.0             | BRP.0   | Baud Rate<br>Prescaler 0        | X                    | Х                                                          |

| Bus timing 1 | BTR1.7             | SAM     | Sampling                        | Х                    | Х                                                          |

|              | BTR1.6             | TSEG2.2 | Time Segment<br>2.2             | X                    | Х                                                          |

|              | BTR1.5             | TSEG2.1 | Time Segment<br>2.1             | X                    | Х                                                          |

|              | BTR1.4             | TSEG2.0 | Time Segment<br>2.0             | X                    | Х                                                          |

|              | BTR1.3             | TSEG1.3 | Time Segment<br>1.3             | X                    | Х                                                          |

|              | BTR1.2             | TSEG1.2 | Time Segment<br>1.2             | X                    | Х                                                          |

|              | BTR1.1             | TSEG1.1 | Time Segment<br>1.1             | X                    | Х                                                          |

|              | BTR1.0             | TSEG1.0 | Time Segment<br>1.0             | Х                    | Х                                                          |

|                    |      |             |                                 | VA                   | ALUE                                                       |

|--------------------|------|-------------|---------------------------------|----------------------|------------------------------------------------------------|

| REGISTER           | BIT  | SYMBOL      | NAME                            | RESET BY<br>HARDWARE | SETTING<br>BIT CR.0 BY<br>SOFTWARE<br>OR DUE TO<br>BUS-OFF |

| Output<br>control  | OC.7 | OCTP1       | Output Control<br>Transistor P1 | X                    | Х                                                          |

|                    | OC.6 | OCTN1       | Output Control<br>Transistor N1 | X                    | Х                                                          |

|                    | OC.5 | OCPOL1      | Output Control<br>Polarity 1    | X                    | Х                                                          |

|                    | OC.4 | OCTP0       | Output Control<br>Transistor P0 | X                    | Х                                                          |

|                    | OC.3 | OCTN0       | Output Control<br>Transistor N0 | X                    | Х                                                          |

|                    | OC.2 | OCPOL0      | Output Control<br>Polarity 0    | X                    | Х                                                          |

|                    | OC.1 | OCMOD<br>E1 | Output Control<br>Mode 1        | X                    | Х                                                          |

|                    | OC.0 | OCMOD<br>E0 | Output Control<br>Mode 0        | X                    | Х                                                          |

| Transmit<br>buffer | -    | ТХВ         | Transmit Buffer                 | X                    | Х                                                          |

| Receive<br>buffer  | -    | RXB         | Receive Buffer                  | X                    | Х                                                          |

| Clock divider      | -    | CDR         | Clock Divider<br>Register       | 0000000              | X                                                          |

#### Notes (Table 3.8):

- 1. X means that the value of these registers or bits is not influenced.

- 2. Remarks in brackets explain functional meaning.

- 3. Reading the command register will always reflect a binary '11111111'.

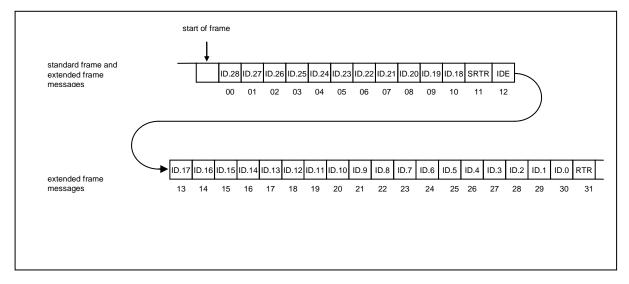

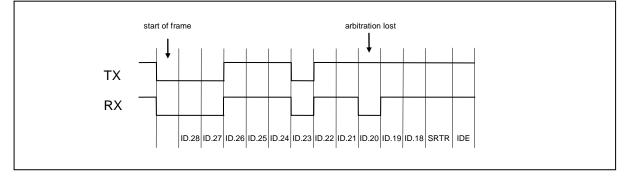

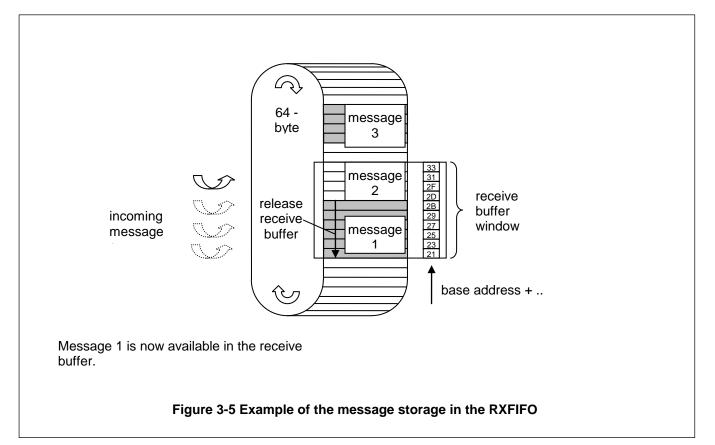

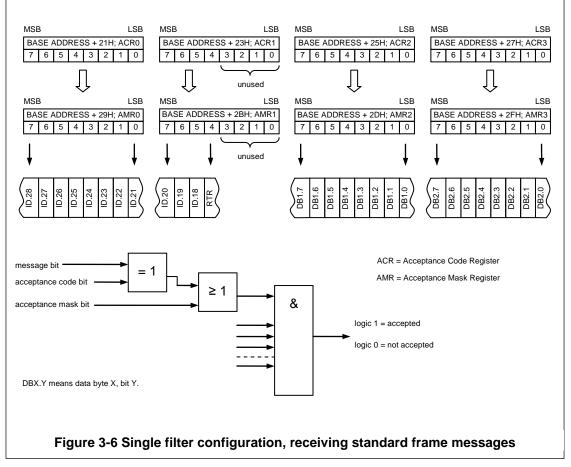

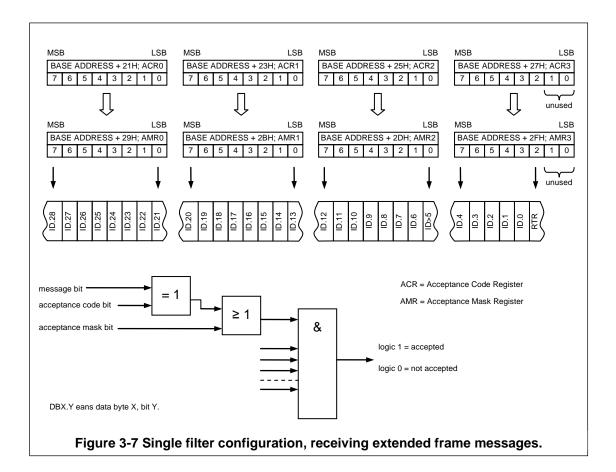

- 4. On bus-off the error interrupt is set, if enabled.