Series IP520-64 Industrial I/O Pack Octal EIA/TIA-232E Communication Module

# **USER'S MANUAL**

ACROMAG INCORPORATED

30765 South Wixom Road P.O. BOX 437 Wixom, MI 48393-7037 U.S.A. Tel: (248) 295-0310 Fax: (248) 624-9234

Copyright 1998, Acromag, Inc., Printed in the USA. Data and specifications are subject to change without notice.

8500-595-D11M004

The information contained in this manual is subject to change without notice. Acromag, Inc. makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Further, Acromag, Inc. assumes no responsibility for any errors that may appear in this manual and makes no commitment to update, or keep current, the information contained in this manual. No part of this manual may be copied or reproduced in any form, without the prior written consent of Acromag, Inc.

| Tab | le of Contents                              | Page |

|-----|---------------------------------------------|------|

| 1.0 | GENERAL INFORMATION                         | 2    |

|     | KEY IP520 FEATURES                          | 2    |

|     | INDUSTRIAL I/O PACK INTERFACE FEATURES      | 3    |

|     | SIGNAL INTERFACE PRODUCTS                   | 3    |

|     | INDUSTRIAL I/O PACK SOFTWARE LIBRARY        | 3    |

|     | IP MODULE OLE CONTROL SOFTWARE              | 4    |

|     | IP MODULE VxWORKS SOFTWARE                  | 4    |

| 2.0 | PREPARATION FOR USE                         | 4    |

|     | UNPACKING AND INSPECTION                    | 4    |

|     | CARD CAGE CONSIDERATIONS                    | 4    |

|     | BOARD CONFIGURATION                         | 4    |

|     | CONNECTORS                                  | 4    |

|     | IP Field I/O Connector (P2)                 | 4    |

|     | Noise and Grounding Considerations          | 5    |

|     | IP Logic Interface Connector (P1)           | 5    |

| 3.0 | PROGRAMMING INFORMATION                     | 6    |

| 3.0 | ADDRESS MAPS                                | 6    |

|     | RBR - Receiver Buffer Register              | 7    |

|     |                                             | 7    |

|     | THR - Transmitter Holding Register          | 7    |

|     | DLL & DLM - Divisor Latch Registers         | 8    |

|     | IER - Interrupt Enable Register             | -    |

|     | ISR - Interrupt Status Register             | 9    |

|     | FCR - FIFO Control Register                 | 9    |

|     | LCR - Line Control Register.                | 10   |

|     | MCR - Modem Control Register                | 10   |

|     | LSR - Line Status Register                  | 11   |

|     | MSR - Modem Status Register                 | 11   |

|     | SCR - Scratch Pad/Interrupt Vector Register | 12   |

|     | Enhanced Register Set                       | 12   |

|     | EFR - Enhanced Feature Register             | 12   |

|     | XON/XOFF - 1,2 Registers                    | 13   |

|     | Identification Space                        | 13   |

|     | THE EFFECT OF RESET                         | 13   |

|     | IP520 PROGRAMMING CONSIDERATIONS            | 14   |

|     | FIFO Polled-Mode                            | 15   |

|     | FIFO Interrupt Mode                         | 15   |

|     | Loopback Mode Operation                     | 15   |

|     | Interrupt Generation                        | 15   |

|     | Software Flow Control                       | 16   |

|     | Hardware Flow Control                       | 16   |

|     | Programming Example                         | 16   |

| 4.0 | THEORY OF OPERATION                         | 17   |

|     | RS232 SERIAL INTERFACE                      | 17   |

|     | IP520 OPERATION                             | 19   |

|     | LOGIC/POWER INTERFACE                       | 19   |

| 5.0 | SERVICE AND REPAIR                          | 19   |

|     | SERVICE AND REPAIR ASSISTANCE               | 19   |

|     | PRELIMINARY SERVICE PROCEDURE               | 19   |

| 6.0 | SPECIFICATIONS                              | 19   |

|     | PHYSICAL                                    | 19   |

|     | ENVIRONMENTAL                               | 19   |

|     | UART                                        | 20   |

|     | RS232 PORTS.                                | 20   |

|     | RS232 TRANSMITTER OUTPUTS                   | 20   |

|     | RS232 RECEIVERS INPUTS                      | 20   |

|     | INDUSTRIAL I/O PACK COMPLIANCE              | 20   |

|     |                                             |      |

| TERMINA                                                  | X<br>MODEL 5025-550-X. & 5025-551-X<br>TION PANEL: MODEL 5025-552<br>ION MODULE: MODEL TRANS-GP                                                                                                           | 21<br>21<br>21<br>21                           |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 4501-709<br>4501-710<br>4501-462<br>4501-463<br>4501-464 | 3S<br>IP MECHANICAL ASSEMBLY<br>IP520 BLOCK DIAGRAM<br>RS232 INTERFACE DIAGRAM<br>CABLE 5025-550 (NON-SHIELDED)<br>CABLE 5025-551 (SHIELDED)<br>TERMINATION PANEL 5025-552<br>TRANSITION MODULE TRANS-GP. | Page<br>22<br>23<br>24<br>25<br>26<br>27<br>28 |

#### IMPORTANT SAFETY CONSIDERATIONS

It is very important for the user to consider the possible adverse effects of power, wiring, component, sensor, or software failures in designing any type of control or monitoring system. This is especially important where economic property loss or human life is involved. It is important that the user employ satisfactory overall system design. It is agreed between the Buyer and Acromag, that this is the Buyer's responsibility.

Trademarks are the property of their respective owners.

## 1.0 GENERAL INFORMATION

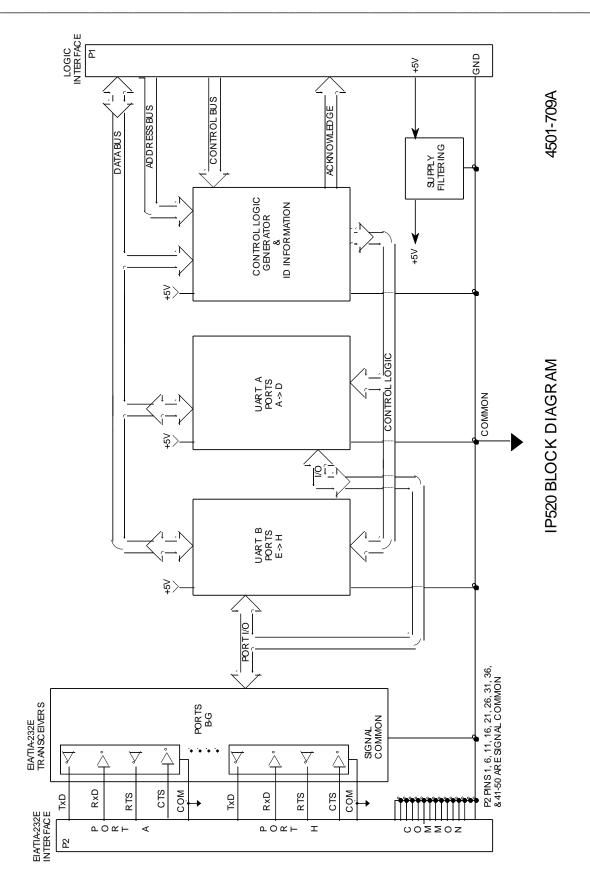

The Industrial I/O Pack (IP) Series IP520 module provides eight EIA/TIA-232E serial communication ports for interfacing to the VMEbus, PCIbus, or ISAbus, according to your carrier board. Up to five units may be mounted on the PCIbus carrier board to provide up to 40 asynchronous serial ports per PCI system slot.

The transmit and receive paths of each channel include generous 64-byte FIFO buffers to minimize CPU interaction. Character size, stop bits, parity, and baud rate are software configurable. Prioritized interrupt generation is also supported for transmit, receive, line status, and data set conditions. The IP520 utilizes state of the art Surface-Mounted Technology (SMT) to achieve its wide functionality and is an ideal choice for a wide range of industrial communication interface applications that require a highly reliable, high-performance interface at a low cost.

The IP520 is available in standard and extended temperature range modules. The IP520-64 model is the standard temperature range (0 to 70°C) version. The IP520-64E model is the extended temperature range (-40°C to +85°C) version.

#### **KEY IP520 FEATURES**

- High Density Provides programmable control of eight EIA/TIA-232E serial ports. Four units mounted on a VMEbus or ISAbus carrier board provide 32 serial channels in a single system slot. On the PCIbus carrier, up to five units may be mounted to provide up to 40 asynchronous serial ports per PCI system slot.

- 64-Character FIFO Buffers Both the transmit and receive channels of each serial port provide 64-byte data buffering to reduce CPU interactions and interrupts. This allows the external processor to handle more tasks within a given time.

- **Programmable Character Size** Each serial port is software programmable for 5, 6, 7, or 8 bit character sizes.

- Programmable Stop Bits Each serial port allows 1, 1-1/2, or 2 stop-bits to be added to, or deleted from, the serial data stream.

- Programmable Parity Generation & Detection Even, Odd, or No Parity generation and detection is supported.

- Line-Break Generation & Detection provision for sending and detecting the line break character is provided.

- False Start Bit Detection Prevents the receiver from assembling false data characters due to low-going noise spikes on the RxD input line.

- Programmable Baud Rate The internal baud rate generator allows the 230.4K maximum baud rate to be divided by any divisor between 1 and 2<sup>(16-1)</sup>, providing support for all standard baud rates.

- Interrupt Support Individually controlled transmit empty, receive ready, line status, data set, & flow control interrupts may be generated. Unique interrupts can be assigned to each port. Interrupts use a priority shifting scheme based on the last interrupt serviced, preventing the continuous interrupts of one port from blocking the interrupts of another port.

- Individual Modem Control Signals Each serial channel includes a modem-control and modem-status register and provides EIA/TIA-232E modem line support, including RTS, and CTS.

- Internal Diagnostic Capabilities Loopback controls for communication link fault isolation are included. Break, parity, overrun, and framing error simulation is also possible.

- Compatible with Industry Standard UARTs The UART of this IP module is a compatible with the industry standard ST16C554/654, ST68C554/654, and TL16C544.

Additionally, this device can operate in a 16C450 UART family software compatible mode. The transmit and receive channels are double-buffered in this mode. Hold and shift registers eliminate the need for precise synchronization between the host CPU and the serial data.

- Software Flow Control One or two sequential receive data characters are compared to a programmed Xon or Xoff character value. Data transmission can be suspended or resumed via software flow control.

- Hardware Flow Control The CTS signal is monitored for remote buffer overflow indication and will suspend transmissions if CTS becomes active. The RTS signal is monitored for local buffer overflows upon the FIFO reaching the programmed trigger level.

- Sleep Mode -The UART can be set via register control to a special sleep mode to reduce power consumption when the chip is not being used.

#### INDUSTRIAL I/O PACK INTERFACE FEATURES

- High density Single-size, industry standard, IP module footprint. Four units mounted on a carrier board provide up to 32 serial ports in a single system slot.

- Local ID Each IP module has its own 8-bit ID information which is accessed via data transfers in the "ID Read" space.

- **8-bit I/O** Port register Read/Write is performed through 8-bit data transfer cycles in the IP module I/O space.

- High Speed Access times for all data transfer cycles are described in terms of "wait" states - 1 wait state is required for reading/writing channel data, 2 wait states for interrupt select cycles, and 0 wait states for reading the ID space (see the Specifications section for detailed information).

#### SIGNAL INTERFACE PRODUCTS

(See Appendix for more information on compatible products)

This IP module will mate directly to any industry standard IP carrier board (including Acromag's AVME9630/9660 3U/6U nonintelligent VMEbus carrier boards). Additionally, PC/AT carrier boards are also supported (see the Acromag Model APC8620 PCIbus carrier board). A wide range of other Acromag IP modules are available to serve your signal conditioning and interface needs.

**Note:** Since all connections to field signals are made through the carrier board which passes them to the individual IP modules, you should consult the documentation of your carrier board to ensure compatibility with the following interface products.

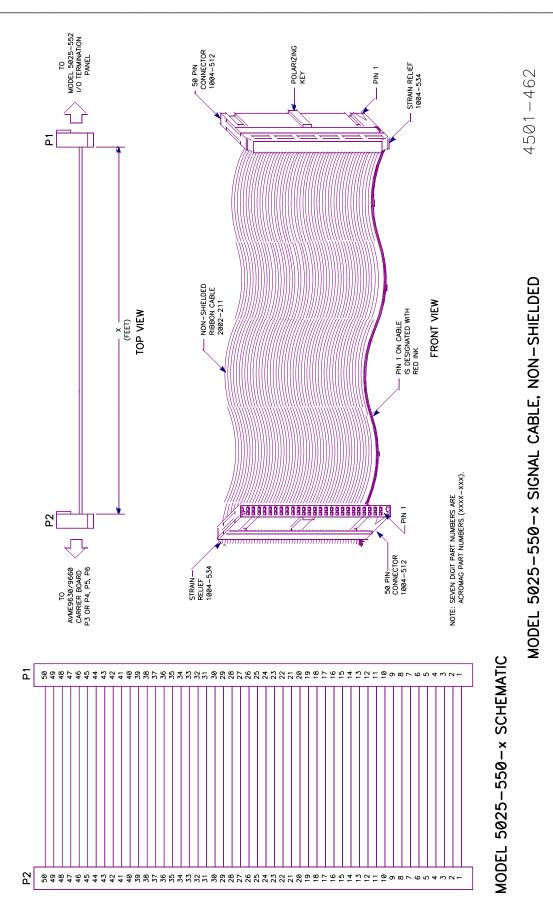

#### Cables:

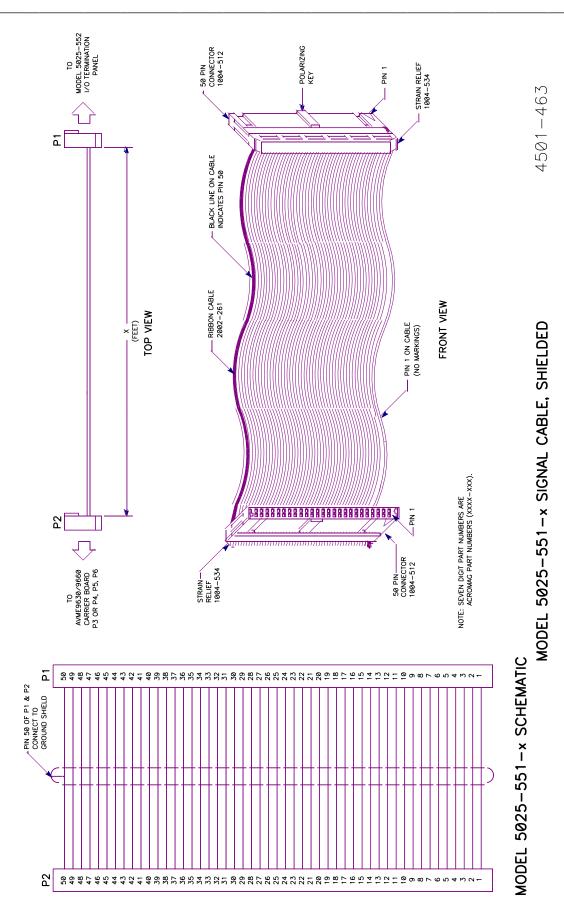

Model 5025-551-X (Shielded Cable), or Model 5025-550-X (Non-Shielded Cable): A Flat 50-pin cable with female connectors at both ends for connecting AVME9630/9660, APC8610, or APC8620 carrier boards, to Model 5025-552 termination panels. The unshielded cable is recommended for digital I/O, while the shielded cable is recommended for optimum performance with precision analog I/O applications. The "-X" suffix of the model number is used to indicate the length in feet.

#### **Termination Panels:**

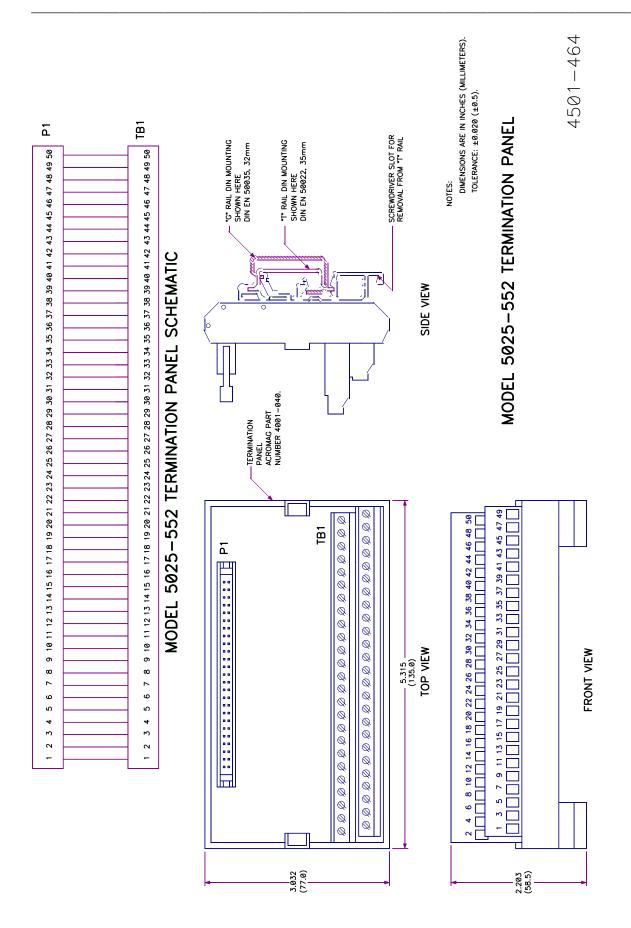

Model 5025-552: A DIN-rail mountable panel that provides 50 screw terminals for universal field I/O termination. Connects to Acromag AVME9630/9660, APC8610, or APC8620 carrier boards, via flat 50-pin ribbon cable (Model 5025-550-X or 5025-551-X).

#### Transition Module:

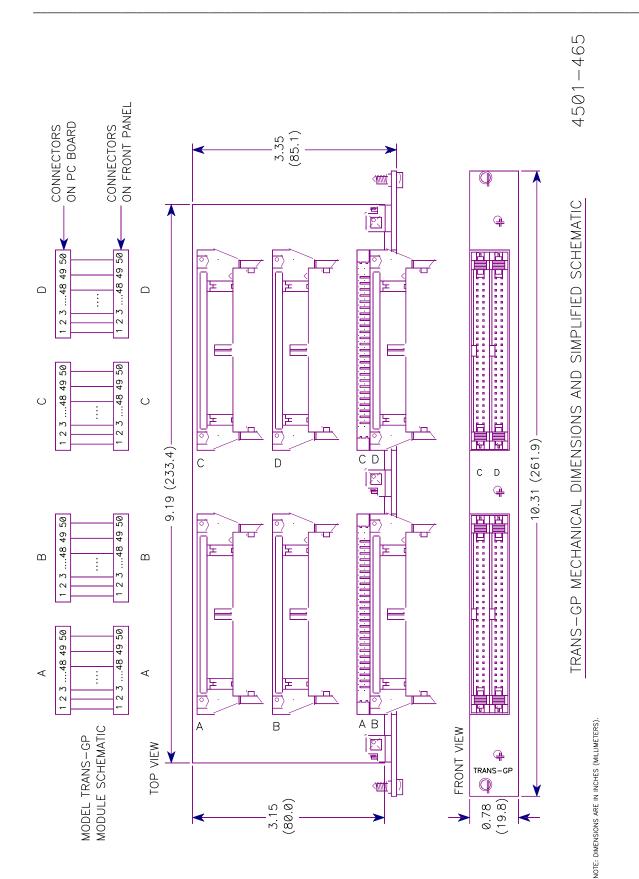

Model TRANS-GP: This module repeats field I/O connections of IP modules A through D for rear exit from a VMEbus card cage. It is available for use in card cages which provide rear exit for I/O connections via transition modules (transition modules can only be used in card cages specifically designed for them). It is a double-height (6U), single-slot module with front panel hardware adhering to the VMEbus mechanical dimensions, except for shorter printed circuit board depth. It connects to Acromag Termination Panel 5025-552 from the rear of the card cage, and to AVME9630/9660 boards within the card cage, via flat 50-pin ribbon cable (cable Model 5025-550 or 5025-551).

#### INDUSTRIAL I/O PACK SOFTWARE LIBRARY

Acromag provides an Industrial I/O Pack Software Library diskette to simplify communication with the board (Model IPSW-LIB-M03, MSDOS format). Example software functions are provided. All functions are written in the "C" programming language and can be linked to your application. Refer to the "README.TXT" file in the root directory and the "INFO520.TXT" file in the "IP520" subdirectory on the diskette for more details.

#### IP MODULE OLE CONTROL SOFTWARE

Acromag provides a software product (sold separately) consisting of IP module OLE (Object Linking and Embedding) drivers for Windows 95®, and Windows NT® compatible application programs (Model IPSW-OLE-PCI, MSDOS format). This software provides individual drivers that allow Acromag IP modules and our personal computer carriers to be easily integrated into Windows® application programs, such as Visual C++™, Visual Basic®, Borland Delphi®, Microsoft® Office® 97 applications and others. The OLE controls provide a high-level interface to IP modules, eliminating the need to perform low-level reads/writes of registers, and the writing of interrupt handlers-all the complicated details of programming are handled by the OLE controls. These functions are intended for use in conjunction with an Acromag personal computer carrier and consist of a Carrier OLE Control, and an OLE control for each Acromag IP module as well as a generic OLE control for non-Acromag IP modules.

#### **IP MODULE VxWORKS SOFTWARE**

Acromag provides a software product (sold separately) consisting of IP module VxWorks® drivers. This software (Model IPSW-API-VXW MSDOS format) is composed of VxWorks® (real time operating system) libraries for all Acromag IP modules and carriers including the AVME9660/9630, APC8610, and APC8620. The software is implemented as a library of "C" functions which when linked with existing user code makes possible simple control of all Acromag IP modules and carriers.

#### 2.0 PREPARATION FOR USE

#### UNPACKING AND INSPECTION

Upon receipt of this product, inspect the shipping carton for evidence of mishandling during transit. If the shipping carton is badly damaged or water stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is absent when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, refer to the Acromag Service Policy to obtain return instructions. It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be

This board is physically protected with packing material and electrically protected with an anti static bag during shipment. However, it is recommended that the board be visually inspected for evidence of mishandling prior to applying power.

The board utilizes static sensitive components and should only be handled at a static-safe workstation.

#### CARD CAGE CONSIDERATIONS

Refer to the specifications for loading and power requirements. Be sure that the system power supplies are able to accommodate the power requirements of the carrier board, plus the installed IP modules, within the voltage tolerances specified.

IMPORTANT: Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature.

The dense packing of the IP modules to the carrier board restricts air flow within the card cage and is cause for concern. Adequate air circulation must be provided to prevent a temperature rise above the maximum operating temperature and to prolong the life of the electronics. If the installation is in an industrial environment and the board is exposed to environmental air, careful consideration should be given to air-filtering.

#### **BOARD CONFIGURATION**

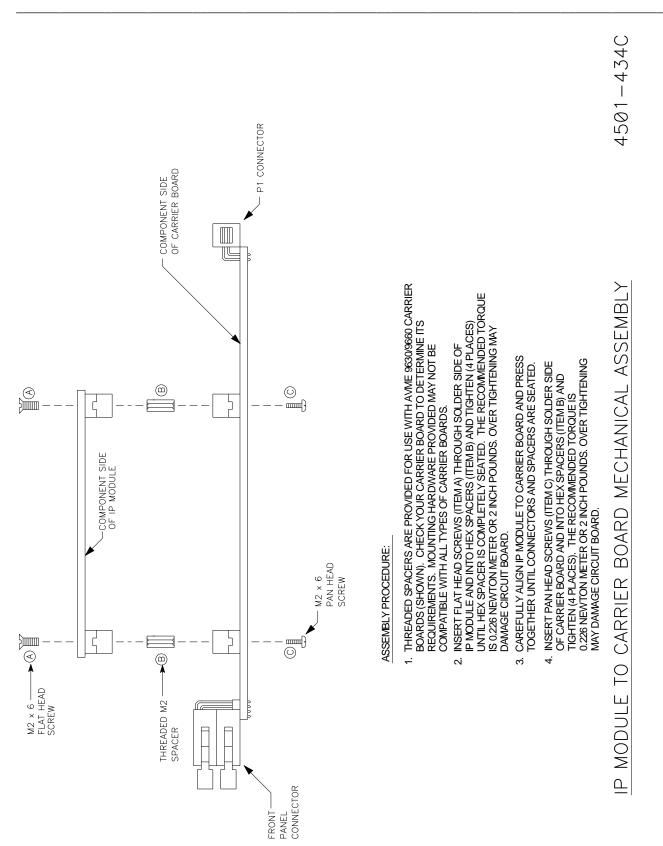

Power should be removed from the board when installing IP modules, cables, termination panels, and field wiring. Refer to Mechanical Assembly Drawing 4501-434 and the following discussion for configuration and assembly instructions. Model IP520 communication boards have no hardware jumpers or switches to configure.

#### CONNECTORS

Connectors of the IP520 module consist of one IP module field I/O connector, and one IP module logic connector. These interface connectors are discussed in the following sections.

#### IP Field I/O Connector (P2)

P2 provides the field I/O interface connections for mating IP modules to the carrier board. P2 is a 50-pin female receptacle header (AMP 173279-3 or equivalent) which mates to the male connector of the carrier board (AMP 173280-3 or equivalent). This provides excellent connection integrity and utilizes gold-plating in the mating area. Threaded metric M2 screws and spacers are supplied with the module to provide additional stability for harsh environments (see Mechanical Assembly Drawing 4501-434). The field and logic side connectors are keyed to avoid incorrect assembly.

P2 pin assignments are unique to each IP model (see Table 2.1) and normally correspond to the pin numbers of the field I/O interface connector on the carrier board (you should verify this for your carrier board).

| Pin Description | Number | Pin Description | Number |

|-----------------|--------|-----------------|--------|

| COMMON          | 1      | COMMON          | 26     |

| TXD_A           | 2      | TXD_F           | 27     |

| RXD_A           | 3      | RXD_F           | 28     |

| RTS_A*          | 4      | RTS_F*          | 29     |

| CTS_A*          | 5      | CTS_F*          | 30     |

| COMMON          | 6      | COMMON          | 31     |

| TXD_B           | 7      | TXD_G           | 32     |

| RXD_B           | 8      | RXD_G           | 33     |

| RTS_B*          | 9      | RTS_G*          | 34     |

| CTS_B*          | 10     | CTS_G*          | 35     |

| COMMON          | 11     | COMMON          | 36     |

| TXD_C           | 12     | TXD_H           | 37     |

| RXD_C           | 13     | RXD_H           | 38     |

| RTS_C*          | 14     | RTS_H*          | 39     |

| CTS_C*          | 15     | CTS_H*          | 40     |

| COMMON          | 16     | COMMON          | 41     |

| TXD_D           | 17     | COMMON          | 42     |

| RXD_D           | 18     | COMMON          | 43     |

| RTS_D*          | 19     | COMMON          | 44     |

| CTS_D*          | 20     | COMMON          | 45     |

| COMMON          | 21     | COMMON          | 46     |

| TXD_E           | 22     | COMMON          | 47     |

| RXD_E           | 23     | COMMON          | 48     |

| RTS_E*          | 24     | COMMON          | 49     |

| CTS_E*          | 25     | COMMON          | 50     |

Table 2.1: IP520 Field I/O Pin Connections (P2)

An Asterisk (\*) is used to indicate an active-low signal.

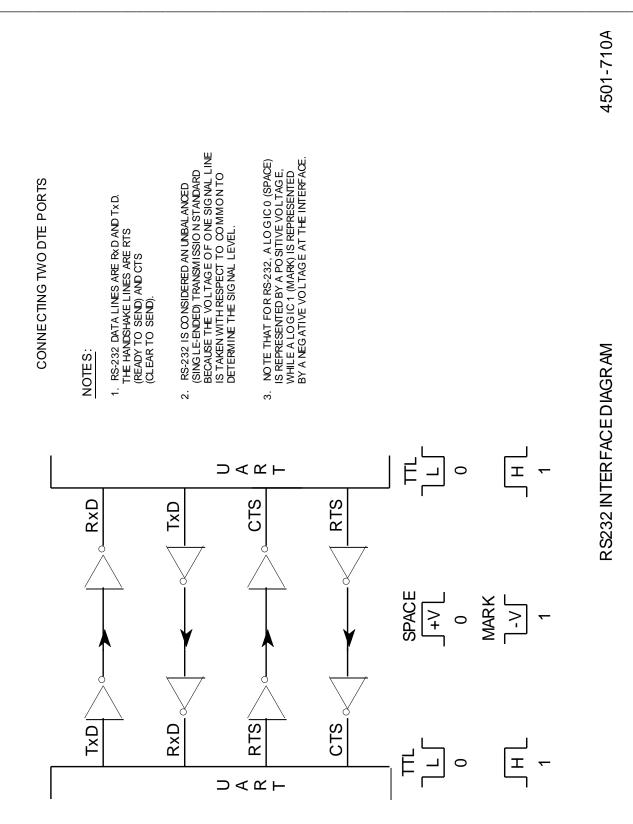

In Table 2.1, a suffix of "\_A", "\_B", "\_C", to "\_H" is appended to each pin label to denote its port association. A brief description of each of the serial port signals at P2 is included below. A complete functional description of all P2 pin functions is included in Section 4.0 (Theory Of Operation).

P2 Pin Signal Descriptions

| SIGNAL                 | DESCRIPTION                                                                                                                                                                                                                            |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxD_A<br>to<br>TxD_H   | Transmit Data Line Output - This is the transmit<br>output data line. In the idle state, this signal line is<br>held in the mark (logic 1) state. During Loopback<br>Mode, the TxD output is internally connected to the<br>RxD input. |

| RxD_A<br>to<br>RxD_H   | Receive Data Line Input - This is the receive data<br>input line. During Loopback Mode, the RxD input is<br>disabled from the external connection and<br>connected to the TxD output internally.                                       |

| RTS_A*<br>to<br>RTS_H* | Ready-to-Send Output - The RTS output is turned<br>on to tell the modem it is ready to send data. This<br>signal can be set low (active) by writing a 1 to the<br>Modem Control Register.                                              |

| CTS_A*<br>to<br>CTS_H* | Clear-to-Send Input - Turned on by the receiving<br>device to indicate it is ready to receive data. The<br>input status of this signal can be read via bit 4 of<br>the Modem Status Register.                                          |

#### Noise and Grounding Considerations

The serial channels of this module are non-isolated and share a common signal ground connection. Further, the IP520 is non-isolated between the logic and field I/O grounds since signal common is electrically connected to the IP module ground. Consequently, the field interface connections are not isolated from the carrier board and backplane. Care should be taken in designing installations without isolation to avoid noise pickup and ground loops caused by multiple ground connections. The signal ground connection at the communication ports are common to the IP interface ground, which is typically common to safety (chassis) ground when mounted on a carrier board and inserted in a backplane. As such, be careful not to attach signal ground to safety ground via any device connected to these ports, or a ground loop will be produced, and this may adversely affect operation.

The communication cabling of the P2 interface carries digital data at a high transfer rate. For best performance, increased signal integrity, and safety reasons, you should isolate these connections away from power and other wiring to avoid noise-coupling and crosstalk interference. Historically, RS-232 communication distances were generally limited to less than 50 feet. Actual distance limits are set by the EIA/TIA-232E driver load capacitance limit (2500pF). In any case, interface cabling and ground wiring should always be kept as short as possible for best performance.

#### IP Logic Interface Connector (P1)

P1 of the IP module provides the logic interface to the mating connector on the carrier board. This connector is a 50-pin female receptacle header (AMP 173279-3 or equivalent) which mates to the male connector of the carrier board (AMP 173280-3 or equivalent). This provides excellent connection integrity and utilizes gold-plating in the mating area. Threaded metric M2 screws and spacers are supplied with the IP module to provide additional stability for harsh environments (see Drawing 4501-434 for assembly details).

#### Table 2.2: Standard Logic Interface Connections (P1)

| Pin Description | Number | Pin Description | Number |

|-----------------|--------|-----------------|--------|

| GND             | 1      | GND             | 26     |

| CLK             | 2      | +5V             | 27     |

| Reset*          | 3      | R/W*            | 28     |

| D00             | 4      | IDSEL*          | 29     |

| D01             | 5      | DMAReq0*        | 30     |

| D02             | 6      | MEMSEL*         | 31     |

| D03             | 7      | DMAReq1*        | 32     |

| D04             | 8      | IntSel*         | 33     |

| D05             | 9      | DMAck0*         | 34     |

| D06             | 10     | IOSEL*          | 35     |

| D07             | 11     | RESERVED        | 36     |

| D08             | 12     | A1              | 37     |

| D09             | 13     | DMAEnd*         | 38     |

| D10             | 14     | A2              | 39     |

| D11             | 15     | ERROR*          | 40     |

| D12             | 16     | A3              | 41     |

| D13             | 17     | INTReq0*        | 42     |

| D14             | 18     | A4              | 43     |

| D15             | 19     | INTReq1*        | 44     |

| BS0*            | 20     | A5              | 45     |

| BS1*            | 21     | STROBE*         | 46     |

| -12V            | 22     | A6              | 47     |

| +12V            | 23     | ACK*            | 48     |

| +5V             | 24     | RESERVED        | 49     |

| GND             | 25     | GND             | 50     |

An Asterisk (\*) is used to indicate an active-low signal. **BOLD ITALIC** Logic Lines are NOT USED by this IP Model. Field and logic side connectors are keyed to avoid incorrect assembly. The pin assignments of P1 are standard for all IP modules according to the Industrial I/O Pack Specification (see Table 2.2). Note that the IP520 does not utilize all of the logic signals defined for the P1 connector and these are indicated in **BOLD ITALICS**.

## 3.0 PROGRAMMING INFORMATION

#### ADDRESS MAPS

This board is addressable in the Industrial Pack I/O space to control the interface configuration, data transfer, and steering logic of eight EIA/TIA-232E serial ports. As such, three types of information are stored in the I/O space: control, status, and data. These registers are listed below along with their mnemonics used throughout this manual.

The I/O space may be as large as 64, 16-bit words (128 bytes) using address lines A1..A6, but the IP520 uses 64 lower byte locations of this space. The I/O space address map for the IP520 is shown in Table 3.1. Note that the base address for the IP module I/O space (see your carrier board instructions) must be added to the addresses shown to properly access the I/O space. All accesses are performed on an 8-bit word basis (D0..D7).

This manual is presented using the "Big Endian" byte ordering format. Big Endian is the convention used in the Motorola 68000 microprocessor family and is the VMEbus convention. In Big Endian, the lower-order byte is stored at oddbyte addresses. Thus, byte accesses are done on odd address locations. The Intel x86 family of microprocessors use the opposite convention, or "Little Endian" byte ordering. Little Endian uses even-byte addresses to store the low-order byte. As such, use of this module on a PC carrier board will require the use of the even address locations to access the 8-bit data, while a VMEbus carrier requires the use of odd address locations.

| SERIAL D  | SERIAL DATA REGISTERS (Per Serial Port): |  |  |  |

|-----------|------------------------------------------|--|--|--|

| RBR       | Receiver Buffer Register                 |  |  |  |

| THR       | Transmitter Holding Register             |  |  |  |

| SERIAL ST | TATUS REGISTERS (Per Serial Port):       |  |  |  |

| LSR       | Line Status Register                     |  |  |  |

| MSR       | Modem Status Register                    |  |  |  |

| ISR       | Interrupt Status Register                |  |  |  |

| SERIAL CO | ONTROL REGISTERS (Per Serial Port):      |  |  |  |

| LCR       | Line Control Register                    |  |  |  |

| FCR       | FIFO Control Register                    |  |  |  |

| MCR       | Modem Control Register                   |  |  |  |

| DLL       | Divisor Latch LSB                        |  |  |  |

| DLM       | Divisor Latch MSB                        |  |  |  |

| IER       | Interrupt Enable Register                |  |  |  |

| SCR       | Scratch Pad/Interrupt Vector Register    |  |  |  |

| EFR       | Enhanced Feature Register                |  |  |  |

| XON-1     | XON-1 Low Byte                           |  |  |  |

| XON-2     | XON-2 High Byte                          |  |  |  |

| XOFF-1    | XOFF-1 Low Byte                          |  |  |  |

| XOFF-2    | XOFF-2 High Byte                         |  |  |  |

Shaded registers are accessible only after writing "BF" to the line Control Register (LCR).

Note that some functions share the same register address. For these items, the address lines are used along with the LCR (Line Control Register) and/or the read and write signals to determine the function required. The DLL and DLM registers are only accessible when LCR bit-7 is set to "1". The EFR, Xon 1,2, and Xoff 1,2 locations are accessible only when the LCR is set to "BF" hex.

The IP520 is an eight port RS232 module. Memory map Table 3.1 lists the addresses and registers corresponding to Port A. Detailed register maps for Ports B to H are not given. Since all registers corresponding to all Ports are listed in the same order, it is possible to determine the address for Ports B to H by using Port A and adding the offset given in the table below. For example, Port E's LCR can be accessed at word address 40 + 06 or 46 hex which is Port A LCR at 06 hex plus Port E Offset at 40 hex.

| PORT | ADDRESS SPACE OFFSET |

|------|----------------------|

| A    | 00                   |

| В    | 10                   |

| С    | 20                   |

| D    | 30                   |

| E    | 40                   |

| F    | 50                   |

| G    | 60                   |

| Н    | 70                   |

Table 3.1: IP520 I/O Space Address (Hex) Memory Map

| Base                     | MSB                                 | LSB                           | LSB LCR  |       |  |  |

|--------------------------|-------------------------------------|-------------------------------|----------|-------|--|--|

| Addr+                    | D15 D08                             | D07 D00                       |          | Addr+ |  |  |

| Serial Port A Registers: |                                     |                               |          |       |  |  |

| 00                       | 1                                   | READ - RBR                    | Bit7     |       |  |  |

|                          | Not Driven <sup>1</sup>             | Port A Receiver               | 0        |       |  |  |

|                          |                                     | Buffer Register               |          | 01    |  |  |

| 00                       | Not Driven <sup>1</sup>             | WRITE - THR                   | Bit7     |       |  |  |

|                          | Not Driven                          | Port A Transmitter            | 0        | 01    |  |  |

| 00                       |                                     | Holding Register<br>R/W - DLL | Bit7     | 01    |  |  |

| 00                       | Not Driven <sup>1</sup>             | Port A Divisor                | 1        |       |  |  |

|                          | Not Driven                          | Latch LSB                     | '        | 01    |  |  |

| 02                       |                                     | R/W - IER                     | Bit7     |       |  |  |

|                          | Not Driven <sup>1</sup>             | Port A Interrupt              | 0        |       |  |  |

|                          |                                     | Enable Register               | -        | 03    |  |  |

| 02                       |                                     |                               | Bit7     |       |  |  |

|                          | Not Driven <sup>1</sup>             | Port A Divisor                | 1        |       |  |  |

|                          | Latch MSB                           |                               |          | 03    |  |  |

| 04                       | 1                                   | READ - ISR                    |          |       |  |  |

|                          | Not Driven <sup>1</sup>             | Port A Interrupt              | N/A      |       |  |  |

|                          |                                     | Status Reg                    | _        | 05    |  |  |

| 04                       | Not Detail                          | WRITE - FCR                   | N1/A     |       |  |  |

|                          | Not Driven <sup>1</sup>             | Port A FIFO                   | N/A      | 05    |  |  |

| 04                       |                                     | Control Reg.<br>R/W - EFR     | BF       | 05    |  |  |

| 04                       | Not Driven <sup>1</sup>             | Port A Enhanced               | ы<br>Нех |       |  |  |

|                          | Feature Register                    |                               | I ICA    | 05    |  |  |

| 06                       |                                     | R/W - LCR                     |          |       |  |  |

|                          | Not Driven <sup>1</sup> Port A Line |                               | N/A      |       |  |  |

|                          |                                     | Register                      | 07       |       |  |  |

| 08                       |                                     | R/W - MCR                     |          |       |  |  |

|                          | Not Driven <sup>1</sup>             | Port A Modem                  | N/A      |       |  |  |

|                          |                                     | Control Reg                   | 09       |       |  |  |

| 08                       | 4                                   | R/W - Xon-1                   | BF       |       |  |  |

|                          | Not Driven <sup>1</sup>             | Low Byte                      | Hex      | 09    |  |  |

| Base    | MSB                     | LSB LCR                                              |                 | Base         |

|---------|-------------------------|------------------------------------------------------|-----------------|--------------|

| Addr+   | D15 D08                 | D07 D00                                              |                 | Addr+        |

| 0A      |                         | R/W - LSR                                            |                 |              |

|         | Not Driven <sup>1</sup> | Port A Line Status                                   | N/A             |              |

| 0A      |                         | Register                                             | BF              | 0B           |

| UA      | Not Driven <sup>1</sup> | R/W - Xon-2<br>High Byte                             | вг<br>Нех       | 0B           |

| 0C      | Not Driven              | R/W - MSR                                            | TIEX            | 00           |

|         | Not Driven <sup>1</sup> | Port A Modem                                         | N/A             |              |

|         | Not Driven              | Status Reg.                                          | IN/A            | 0D           |

| 0C      |                         | R/W - Xoff-1                                         | BF              | •=           |

|         | Not Driven <sup>1</sup> | Low Byte                                             | Hex             | 0D           |

| 0E      |                         | R/W - SCR                                            |                 |              |

|         | Not Driven <sup>1</sup> | Port A Scratch                                       | N/A             |              |

|         |                         | Pad, Interrupt                                       |                 |              |

|         |                         | Vector, FIFO Count                                   |                 | 0F           |

| 0E      | N / D / 1               | R/W - Xoff-2 BF                                      |                 |              |

|         | Not Driven <sup>1</sup> | High Byte Hex                                        |                 | 0F           |

| 10      | Not Detail              | Port B Registers                                     | S _ 3           | 11           |

| .↓      | Not Driven <sup>1</sup> | Organized as Port A <sup>3</sup>                     |                 | $\downarrow$ |

| 1E      |                         |                                                      |                 | 1F           |

| 20      | N / D / 1               | Port C Registers                                     |                 | 21           |

| ↓       | Not Driven <sup>1</sup> | Organized as Port                                    | $\downarrow$    |              |

| 2E      |                         |                                                      | 2F              |              |

| 30      | Not Driven <sup>1</sup> | Port D Registers                                     | 5<br>• 3        | 31           |

| ↓       | Not Driven              | Organized as Port                                    | $\downarrow$    |              |

| 3E      |                         |                                                      |                 | 3F           |

| 40      | Not Driven <sup>1</sup> | Port E Registers                                     | s<br>^3         | 41           |

| ↓       | NOT Driven              | Organized as Port                                    | ↓<br>4 <b>5</b> |              |

| 4E      |                         |                                                      | 4F              |              |

| 50      | Not Driven <sup>1</sup> | Port F Registers<br>Organized as Port A <sup>3</sup> |                 | 51           |

| ↓<br>5E | NOL Driven              | Organized as Port                                    | ↓<br>5F         |              |

| -       |                         | Dant C. Daniatan                                     |                 | -            |

| 60      | Not Driven <sup>1</sup> | Port G Registers<br>Organized as Port A <sup>3</sup> |                 | 61           |

| ↓<br>6E | NOL DIIVEII             | Organized as Port                                    | ↓<br>6F         |              |

| -       |                         | Dort LI Docietary                                    | -               |              |

| 70<br>↓ | Not Driven <sup>1</sup> | Port H Registers<br>Organized as Port                | 71<br>↓         |              |

| 7Ĕ      | NOL DIIVEII             | Organized as Port                                    | ↓<br>7F         |              |

| /E      |                         | 1                                                    | /F              |              |

#### Notes (Table 3.1):

- 1. The upper 8 bits of these registers are not driven. Pullups on the carrier data bus will cause these bits to read high (1's).

- All Reads/Writes to IO space are 1 wait state, Interrupt select cycle is 2 wait states, and ID space reads are 0 wait states.

- 3. To save user manual space the registers corresponding to ports B to H have not been individually shown. The registers of ports B to H are in the address space shown above. To access a register in port H, for example, the offset of 70 hex is added to the address of the corresponding register given in table 3.1. All ports require a 16 byte memory block.

This board operates in two different modes. In one mode, this device remains software compatible with the industry standard 16C450 family of UART's and provides double-buffering of data registers. In the FIFO Mode (enabled via bit 0 of the FCR register), data registers are FIFO-buffered so that read and write operations can be performed while the UART is performing serialto-parallel and parallel-to-serial conversions. Two FIFO modes are possible: FIFO Interrupt Mode and FIFO Polled Mode. Some registers operate differently between the available modes and this is noted in the following paragraphs.

#### RBR - Receiver Buffer Register, Ports A-H (READ Only)

The Receiver Buffer Register (RBR) is a serial port input data register that receives the input data from the receiver shift register and holds from 5 to 8 bits of data, as specified by the character size programmed in the Line Control Register (LCR bits 0 & 1). If less than 8 bits are transmitted, then data is rightjustified to the LSB. If parity is used, then LCR bit 3 (parity enable) and LCR bit 4 (type of parity) are required. Status for the receiver is provided via the Line-Status Register (LSR). When a full character is received (including parity and stop bits), the datareceived indication bit (bit 0) of the LSR is set to 1. The host CPU then reads the Receiver Buffer Register, which resets LSR bit 0 low. If the character is not read prior to a new character transfer between the receiver shift register and the receiver buffer register, the overrun-error status indication is set in LSR bit 1. If there is a parity error, the error is indicated in LSR bit 2. If a stop bit is not detected, a framing error indication is set in bit 3 of the LSR.

Serial asynchronous data is input to the receiver shift register via the receive data line (RxD). From the idle state, this line is monitored for a high-to-low transition (start bit). When the start bit is detected, a counter is reset and counts the 16x clock to 7-1/2 (which is the center of the start bit). The start bit is judged valid if RxD is still low at this point. This is known as false start-bit detection. By verifying the start bit in this manner, it helps to prevent the receiver from assembling an invalid data character due to a low-going noise spike on RxD. If the data on RxD is a symmetrical square wave, the center of the data cells will occur within  $\pm 3.125\%$  of the actual center (providing an error margin of 46.875%). Thus, the start bit can begin as much as one 16x clock cycle prior to being detected.

#### THR - Transmitter Holding Register, Ports A-H (WRITE Only)

The Transmitter Holding Register (THR) is a serial port output data register that holds from 5 to 8 bits of data, as specified by the character size programmed in the Line Control Register. If less than 8 bits are transmitted, then data is entered right-justified to the LSB. This data is framed as required, then shifted to the transmit data line (TxD). In the idle state, TxD is held high. In Loopback Mode, this data is looped back into the Receiver Buffer Register.

The status of the THR is provided in the Line Status Register (LSR). Writing to the THR transfers the contents of the data bus (D7-D0) to the THR, provided that at least one FIFO location is available. The THR empty flag in the LSR register will be set to a logic 1 when at least one FIFO location is available.

#### DLL & DLM - Divisor Latch Registers, Ports A-H (R/W)

The Divisor Latch Registers form the divisor used by the internal baud-rate generator to divide the 14.7456MHz clock to produce an internal sampling clock suitable for synchronization to the desired baud rate. The output of the baud generator (RCLK) is sixteen times the baud rate. Two 8-bit divisor latch registers per port are used to store the divisors in 16-bit binary format. The DLL register stores the low-order byte of the divisor, DLM stores the high-order byte. These registers must be loaded during initialization.

Note that bit 7 of the LCR register must first be set high to access the divisor latch registers (DLL & DLM) during a read/write operation.

Upon loading either latch, a 16-bit baud counter is immediately loaded (this prevents long counts on initial load). The clock may be divided by any divisor from 1 to  $2^{(16-1)}$ . The relationship between the baud rate, the divisor, and the 14.7456MHz clock can be summarized in the following equations:

Divisor =  $\frac{14.7456\text{MHz}}{16 \times \text{Baud Rate} \times \text{MCRDIV}}$

Baud Rate =  $\frac{14.7456 \text{MHz}}{16 \times \text{Divisor} \times \text{MCRDIV}}$

The MCRDIV term represents the state of bit-7 of the MCR (Mode Control Register) as follows:

MCRDIV = 1 If MCR bit-7=0 MCRDIV = 4 If MCR bit-7=1

The following table shows the correct divisor to use for generation of some standard baud rates (based on the 14.7456MHz clock). Note that baud rates up to 921.6K may be configured, but the EIA/TIA-232E drivers of this module limits data rates to 230Kbps maximum for performance within rated specifications. A different external crystal can replace the 14.7456MHz crystal on the circuit board to obtain unique clock rates. You may contact Acromag Applications Engineering to explore options in this area.

| Table 3.2: Baud Rate Divisors | (14.74MHz Clock) |

|-------------------------------|------------------|

|-------------------------------|------------------|

| BAUD RATE      |                | DIVISOR (N) |              |              |

|----------------|----------------|-------------|--------------|--------------|

| MCR<br>Bit-7=1 | MCR<br>Bit-7=0 | Decimal     | DLM<br>(HEX) | DLL<br>(HEX) |

| 50             | 200            | 4608        | 12           | 00           |

| 300            | 1200           | 768         | 03           | 00           |

| 600            | 2400           | 384         | 01           | 80           |

| 1200           | 4800           | 192         | 00           | C0           |

| 2400           | 9600           | 96          | 00           | 60           |

| 3600           | 14,400         | 64          | 00           | 40           |

| 4800           | 19,200         | 48          | 00           | 30           |

| 7200           | 28,800         | 32          | 00           | 20           |

| 9600           | 38,400         | 24          | 00           | 18           |

| 19,200         | 76,800         | 12          | 00           | 0C           |

| 28,800         | 115,200        | 8           | 00           | 08           |

| 38,400         | 153,600        | 6           | 00           | 06           |

| 57,600         | 230,400        | 4           | 00           | 04           |

With respect to this device, the baud rate may be considered equal to the number of bits transmitted per second (bps). The bit rate (bps), or baud rate, defines the bit time. This is the length of time a bit will be held on before the next bit is transmitted. A receiver and transmitter must be communicating at the same bit rate, or data will be garbled. A receiver is alerted to an incoming character by the start bit, which marks the beginning of the character. It then times the incoming signal, sampling each bit as near to the center of the bit time as possible. To better understand the asynchronous timing used by this device, note that the receive data line (RxD) is monitored for a high-to-low transition (start bit). When the start bit is detected, a counter is reset and counts the 16x sampling clock to 7-1/2 (which is the center of the start bit). The receiver then counts from 0 to 15 to sample the next bit near its center, and so on, until a stop bit is detected, signaling the end of the data stream. Use of a sampling rate 16x the baud rate reduces the synchronization error that builds up in estimating the center of each successive bit following the start bit. As such, if the data on RxD is a symmetrical square wave, the center of each successive data cell will occur within  $\pm 3.125\%$  of the actual center (this is 50%  $\div$  16, providing an error margin of 46.875%). Thus, the start bit can begin as much as one 16x clock cycle prior to being detected.

#### IER - Interrupt Enable Register, Ports A-H (R/W)

The Interrupt Enable Register is used to independently enable/ disable the serial port interrupt sources. Each of the eight ports have seven unique interrupt sources which are all mapped to INTREQ0\* of the IP module.

Interrupts are disabled by resetting the corresponding IER bit low (0), and enabled by setting the IER bit high (1). Disabling the interrupt system (IER bits 7-5 and 3-0 low) also inhibits the Interrupt Status Register (ISR) and the interrupt request line (INTREQ0\*). In addition to enabling the desired bits in the IER, bit-3 of the Modem Control Register (MCR) must be set to a logic "1" to enable interrupts.

| IER BIT | INTERRUPT ACTION                                                                                                                                                                                                                                                                                                                                         |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0       | 0 = Disable Interrupt<br>1 = Enable Interrupt<br>This interrupt will be issued when the FIFO has<br>reached the programmed trigger level or is cleared<br>when the FIFO drops below the trigger level in the<br>FIFO mode of operation. Note that the receive FIFO<br>must also be enabled via bit-0 of the FCR for a<br>receive interrupt to be issued. |  |

| 1       | 0 = Disable Interrupt<br>1 = Enable Interrupt<br>This interrupt will be issued whenever the THR is<br>empty and is associated with bit-1 in the LSR.                                                                                                                                                                                                     |  |

| 2       | 0 = Disable Interrupt<br>1 = Enable Interrupt<br>This interrupt will be issued whenever a fully<br>assembled receive character is available.                                                                                                                                                                                                             |  |

| 3       | 0 = Disable Interrupt<br>1 = Enable Interrupt<br>This interrupt will be issued whenever the CTS<br>signal changes state since it was last read.                                                                                                                                                                                                          |  |

| 41      | 0 = Disable Sleep Mode<br>1 = Enable Sleep Mode<br>The clock/oscillator circuit is disabled in sleep mode.<br>Any change of state on CTS will wake-up the UART.<br>The UART will not lose the programmed bits when<br>sleep mode is activated or deactivated. The UART<br>will not enter sleep mode if any interrupts are<br>pending.                    |  |

| IER BIT        | INTERRUPT ACTION                                                                                                                                                                                                                                          |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5 <sup>1</sup> | 0 = Disable the Receive Xoff Interrupt<br>1 = Enable the Receive Xoff Interrupt<br>When software flow control in enabled, and one or<br>two sequential receive data characters match the<br>preprogrammed Xoff 1-2 values an interrupt will be<br>issued. |  |

| 6 <sup>1</sup> | 0 = Disable RTS Interrupt<br>1 = Enable RTS Interrupt. This Interrupt is<br>generated when the RTS pin transitions from a logic<br>0 to a logic 1.                                                                                                        |  |

| 7 <sup>1</sup> | 0 = Disable CTS Interrupt<br>1 = Enable CTS Interrupt. This interrupt will be<br>issued when the CTS pin transitions from a logic 0 to<br>a logic 1.                                                                                                      |  |

#### Notes (Interrupt Enable Register):

1. Bits 4 to 7 are only programmable when the EFR bit 4 is set to "1".

#### ISR - Interrupt Status Register, Ports A-H (READ Only)

The Interrupt Status Register is used to indicate that a prioritized interrupt is pending and the type of interrupt that is pending. Six levels of prioritized interrupts are provided to minimize software interaction. Performing a read cycle on the ISR will provide the user with the highest pending interrupt level to be serviced. No other interrupts are acknowledged until the pending interrupt is serviced. Whenever the interrupt status register is read, the interrupt status is cleared. Note, only the current pending interrupt is cleared by the read. A lower level interrupt may be seen after re-reading the interrupt status bits.

The eight individual ports share the IP module INTREQ0\* signal. Each port has an opportunity to issue an interrupt in a round robin fashion. That is, interrupt vectors are served according to a shifting priority scheme that is a function of the last interrupting port served.

The following interrupt source table shows the data values (bit 0-5) for the six prioritized interrupt levels and the interrupt sources associated with each of these interrupt levels.

| Interrupt Status Register |                          |                                                  |

|---------------------------|--------------------------|--------------------------------------------------|

| PRIORITY<br>LEVEL         | ISR BITS<br>Bit5 to Bit0 | Source of the Interrupt                          |

| 1                         | 000110                   | Receiver Line Status (see LSR bits 1-4)          |

| 2                         | 000100                   | Received Data Ready or Trigger<br>Level reached. |

| 2                         | 001100                   | Receive Data Time Out.                           |

| 3                         | 000010                   | Transmitter Holding Register<br>Empty            |

| 4                         | 000000                   | MSR (Modem Status Register)                      |

| 5                         | 010000                   | Received Xoff signal special<br>character        |

| 6                         | 100000                   | CTS, RTS change of state                         |

#### Notes (Interrupt Status Register):

1. Bit 4 of the EFR (Enhanced Feature Register) must be set to a logic "1" to unlock access to bits 4 and 5 of this ISR register.

Note that ISR bit 0 can be used to indicate whether an interrupt is pending (bit 0 low when interrupt is pending). ISR bits 1 & 2 are used to indicate the highest priority interrupt pending. ISR bit 3 is always logic 0 in the 16C450 mode. ISR bit 3 is set along with bit 2 when in the FIFO mode and a timeout interrupt is pending. Bit 4 set indicates a Xoff/special character detected interrupt pending. Bit 5 indicates a pending interrupt due to a change of state on the CTS or RTS signals.

Bits 6 and 7 are set when bit 0 of the FIFO Control Register is set to 1. A power-up or system reset sets ISR bit 0 to logic "1", and bits 1 to 7 to logic "0".

## FCR - FIFO Control Register, Ports A-H (WRITE Only)

This write-only register is used to enable and clear the FIFO buffers, set the transmit/receive FIFO trigger levels, and select the type of DMA signaling (DMA is <u>NOT</u> supported by this model).

#### **FIFO Control Register**

| 0 When set to "1", this bit enables both the Tx and Rx<br>FIFO's. All bytes in both FIFO's can be cleared by<br>resetting this bit to 0. Data is cleared automatically<br>from the FIFO's when changing from FIFO mode to<br>the alternate (16C450) mode and visa-versa. This |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| resetting this bit to 0. Data is cleared automatically from the FIFO's when changing from FIFO mode to                                                                                                                                                                        | 0    |

| from the FIFO's when changing from FIFO mode to                                                                                                                                                                                                                               |      |

| 00                                                                                                                                                                                                                                                                            |      |

| the alternate (16C450) mode and visa-versa. This                                                                                                                                                                                                                              |      |

|                                                                                                                                                                                                                                                                               |      |

| bit must be a "1" when other FCR bits are written to                                                                                                                                                                                                                          |      |

| or they will not be programmed.                                                                                                                                                                                                                                               |      |

| 1 When set to "1", this bit clears all bytes in the Rx-                                                                                                                                                                                                                       | 1    |

| FIFO and the resets counter logic to 0 (this does                                                                                                                                                                                                                             |      |

| not clear the shift register).                                                                                                                                                                                                                                                |      |

| 2 When set to "1", this bit clears all bytes in the Tx-                                                                                                                                                                                                                       | 2    |

| FIFO and resets the counter logic to 0 (this does                                                                                                                                                                                                                             |      |

| not clear the shift register).                                                                                                                                                                                                                                                |      |

| 3 When set to "1", this bit sets DMA Signal from                                                                                                                                                                                                                              | 3    |

| Mode 0 to Mode 1, if FIFO Control Register Bit 0 =                                                                                                                                                                                                                            |      |

| 1 (DMA Not Supported)                                                                                                                                                                                                                                                         |      |

| 5,4 <sup>1</sup> These bits are used to set the trigger level for the                                                                                                                                                                                                         | 5,4' |

| transmit FIFO interrupt. An interrupt will be issued                                                                                                                                                                                                                          |      |

| when the number of characters in the FIFO drops                                                                                                                                                                                                                               |      |

| below the selected trigger level. One of four trigger                                                                                                                                                                                                                         |      |

| levels can be selected.                                                                                                                                                                                                                                                       |      |

| bit 5 bit 4 Trigger Level                                                                                                                                                                                                                                                     |      |

| 0 0 08                                                                                                                                                                                                                                                                        |      |

| 0 1 16                                                                                                                                                                                                                                                                        |      |

| 1 0 32                                                                                                                                                                                                                                                                        |      |

|                                                                                                                                                                                                                                                                               | 7.0  |

| 7,6 These bits are used to set the trigger level for the                                                                                                                                                                                                                      | 7,6  |

| receiver FIFO interrupt. An interrupt is generated                                                                                                                                                                                                                            |      |

| when the number of characters in the FIFO equals                                                                                                                                                                                                                              |      |

| the programmed trigger level. One of four trigger levels can be selected.                                                                                                                                                                                                     |      |

| bit 7 bit 6 Trigger Level                                                                                                                                                                                                                                                     |      |

|                                                                                                                                                                                                                                                                               |      |

| 0 1 16                                                                                                                                                                                                                                                                        |      |

| 1 0 56                                                                                                                                                                                                                                                                        |      |

| 1 1 60                                                                                                                                                                                                                                                                        |      |

#### Notes (FIFO Control Register):

1. Bits 4 and 5 are only programmable when the EFR bit 4 is set to "1".

A power-up or system reset sets all FCR bits to 0.

## LCR - Line Control Register, Ports A-H (Read/Write)

The Line Control Register is used to specify the asynchronous data communication format. The word length, the number of stop bits, and the parity are selected by writing the appropriate bits in this register.

The individual bits of this register control the format of the data character as follows:

#### Line Control Register

| LCR Bit | FUNCTION         | PROGRAMMING                                            |

|---------|------------------|--------------------------------------------------------|

| 1,0     | Word             | 0.0 = 5 Data Bits $0.1 = 6$ Data Bits                  |

| 1,0     |                  | 10 = 7 Data Bits $11 = 8$ Data Bits $11 = 8$ Data Bits |

| 0       | Length Sel.      |                                                        |

| 2       | Stop Bit         | 0 = 1 Stop Bit                                         |

|         | Select           | 1 = 1.5 Stop Bits if 5 data bits; 2 Stop               |

| 0       | Devite           | Bits if 6, 7, or 8 data bits selected.                 |

| 3       | Parity<br>Enable | 0 = Parity Disabled 1 = Parity<br>Enabled              |

|         | Enable           | A parity bit is generated and checked                  |

|         |                  | for between the last data word bit and                 |

|         |                  | the stop bit.                                          |

| 4       | Even-Parity      | 0 = Odd Parity                                         |

| 4       | Select           |                                                        |

| _       |                  | 1 = Even Parity                                        |

| 5       | Stick Parity     | 0 = Disabled, 1 = Enabled                              |

|         |                  | When parity is enabled, stick parity                   |

|         |                  | causes the transmission and                            |

|         |                  | reception of a parity bit to be in the                 |

|         |                  | opposite state from the value                          |

|         |                  | selected via bit 4. This is used as a                  |

|         |                  | diagnostic tool to force parity to a                   |

|         |                  | known state and allow the receiver to                  |

|         |                  | check the parity bit in a known state.                 |

| 6       | Break            | 0 = Break Disabled, 1 = Break                          |

| Ũ       | Control          | Enabled                                                |

|         | Control          | When break is enabled, the serial                      |

|         |                  | output line (TxD) is forced to the                     |

|         |                  |                                                        |

|         |                  | space state (low). This bit acts only                  |

|         |                  | on the serial output and does not                      |

|         |                  | affect transmitter logic. For example,                 |

|         |                  | if the following sequence is used, no                  |

|         |                  | invalid characters are transmitted due                 |

|         |                  | to the presence of the break.                          |

|         |                  | <ol> <li>Load a zero byte in response to</li> </ol>    |

|         |                  | the Transmitter Holding Register                       |

|         |                  | Empty (THRE) status indication.                        |

|         |                  | 2. Set the break in response to the                    |

|         |                  | next THRE status indication.                           |

|         |                  | 3. Wait for the transmitter to become                  |

|         |                  | idle when the Transmitter Empty                        |

|         |                  | status signal is set high (TEMT=1);                    |

|         |                  | then clear the break when normal                       |

|         |                  | transmission has to be restored.                       |

| 7       | DLL/DLM          | 0 = Access Receiver Buffer                             |

|         | and EFR          | 1 = Allow Access to Divisor Latches                    |

|         | Enable Bit       | (DLL & DLM) and Enhanced Feature                       |

|         | 2.10010 810      | Register enabled (EFR).                                |

|         |                  |                                                        |

Note that bit 7 must be set high to access the divisor latch registers DLL & DLM of the baud rate generator or access the Enhanced Feature Register (EFR). Bit 7 must be low to access the Receiver Buffer Register (RBR), the Transmitter Holding Register (THR), or the Interrupt Enable Register (IER). A powerup or system reset sets all LCR bits to 0. A detailed discussion of word length, stop bits, parity, and the break signal is included in Section 4.0 (Theory of Operation).

#### MCR - Modem Control Register, Ports A-H (R/W)

The Modem Control register controls the interface with the modem or data set as described below. RTS is directly controlled by a control bit in this register (a high input asserts this signal). **Bit-3 of this register must be set to a logic "1" to enable the corresponding port to issue an interrupt.**

| Modem Control Register |                                  |                                                                                                                                                                                    |  |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MCR Bit                | FUNCTION                         | PROGRAMMING                                                                                                                                                                        |  |

| 0                      | Not Used                         | No Effect on External Operation                                                                                                                                                    |  |

| 1                      | Ready to Send<br>Output (RTS)    | 0 = RTS* Not Asserted (Inactive)<br>1 = RTS* Asserted (Active)                                                                                                                     |  |

| 2                      | Not Used                         | No Effect on External Operation                                                                                                                                                    |  |

| 3                      | Port Interrupt<br>Disable/Enable | <ul> <li>0 = Interrupt Disabled for this port.</li> <li>1 = Interrupt Enabled for this port.</li> </ul>                                                                            |  |

| 4                      | Loop-back <sup>1</sup>           | 0 = Loop-back Disabled<br>1 = Loop-back Enabled                                                                                                                                    |  |

| 5 <sup>2</sup>         | Xon Control                      | 0 = Disable Xon<br>1 = Enable any Xon function. In<br>this mode any RX character<br>received will enable Xon.                                                                      |  |

| 6 <sup>2</sup>         | Not Used                         | Must be logic 0                                                                                                                                                                    |  |

| 7 <sup>2</sup>         | Divide by Four                   | 0 = Divide by one. The crystal<br>frequency is unchanged.<br>1 = Divide by four. After the<br>crystal frequency is divided by 16<br>it is further divided by 4 (see<br>Table 3.2). |  |

#### Notes (Modem Control Register):

- 1. MCR Bit 4 provides a local loopback feature for diagnostic testing of the UART channel. When set high, the UART serial output (connected to the TXD driver) is set to the marking (logic 1 state), and the UART receiver serial data input is disconnected from the RxD receiver path. The output of the UART transmitter shift register is then looped back into the receiver shift register input. The control input (CTS) is disconnected from its receiver input path. The control output (RTS) is internally connected to the control input DSR (while its associated pin is forced to its high/ inactive state). Thus, in the loopback diagnostic mode, transmitted data is immediately received, permitting the host processor to verify the transmit and receive data paths of the selected serial channel. In this mode, interrupts are generated by controlling the state of the four lower order MCR bits internally, instead of by the external hardware paths. However, no interrupt requests or interrupt vectors are actually served in loopback mode, and interrupt pending status is only reflected internally.

- Bits 5-7 are only programmable when the EFR bit 4 is set to "1". The programmed values for these bits are latched when EFR bit 4 is cleared, preventing existing software from inadvertently overwriting the extended functions. However, these MCR bits cannot be set if the LCR is set to BF hex.

A power-up or system reset sets all MCR bits to 0.

## LSR - Line Status Register, Ports A-H (Read/Write-Restricted)